# DESIGN AND CODE OPTIMIZATION FOR SYSTEMS WITH NEXT-GENERATION RACETRACK MEMORIES

# Dissertation

for the purpose of obtaining the doctoral degree (Dr.-Ing.) at Technische Universität Dresden, publicly defended on Monday 25 April 2022 at 13:30 o'clock

by

# Asif Ali Khan

M.Sc., Computer Systems Engineering, born in Nowshera, Pakistan.

# Supervised by:

Prof. Dr.-Ing. Jeronimo Castrillon Chair for Compiler Constructioin, Technische Universität Dresden, Dresden, Germany.

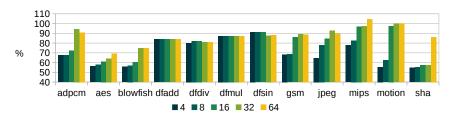

# Composition of the doctoral committee:

Prof. Dr.-Ing. Jeronimo Castrillon (Reviewer)

Prof. Dr.-Ing. Wolfgang Lehner (Chair, TU Dresden)

Prof. Dr. Yiran Chen (Reviewer, Duke University)

Prof. Dr. Akash Kumar (Fachreferent, TU Dresden)

Prof. Dr.-Ing. Horst Schirmeier (Member, TU Dresden)

Dedicated to my family and friends who inspired this dissertation but will never read it.

With the rise of computationally expensive application domains such as machine learning, genomics, and fluids simulation, the quest for performance and energy-efficient computing has gained unprecedented momentum. The significant increase in computing and memory devices in modern systems has resulted in an unsustainable surge in energy consumption, a substantial portion of which is attributed to the memory system. The scaling of conventional memory technologies and their suitability for the next-generation system is also questionable. This has led to the emergence and rise of *nonvolatile memory* (NVM) technologies. Today, in different development stages, several NVM technologies are competing for their rapid access to the market.

Racetrack memory (RTM) is one such nonvolatile memory technology that promises SRAM-comparable latency, reduced energy consumption, and unprecedented density compared to other technologies. However, *racetrack memory* (RTM) is sequential in nature, i.e., data in an RTM cell needs to be *shifted* to an access port before it can be accessed. These shift operations incur performance and energy penalties. An ideal RTM, requiring at most one shift per access, can easily outperform SRAM. However, in the worst-cast shifting scenario, RTM can be an order of magnitude slower than SRAM.

This thesis presents an overview of the RTM device physics, its evolution, strengths and challenges, and its application in the memory subsystem. We develop tools that allow the programmability and modeling of RTM-based systems. For shifts minimization, we propose a set of techniques including optimal, near-optimal, and evolutionary algorithms for efficient scalar and instruction placement in RTMs. For array accesses, we explore schedule and layout transformations that eliminate the longer overhead shifts in RTMs. We present an automatic compilation framework that analyzes static control flow programs and transforms the loop traversal order and memory layout to maximize accesses to consecutive RTM locations and minimize shifts. We develop a simulation framework called *RTSim* that models various RTM parameters and enables accurate architectural level simulation.

Finally, to demonstrate the RTM potential in non-Von-Neumann in-memory computing paradigms, we exploit its device attributes to implement logic and arithmetic operations. As a concrete use-case, we implement an entire hyperdimensional computing framework in RTM to accelerate the language recognition problem. Our evaluation shows considerable performance and energy improvements compared to conventional Von-Neumann models and state-of-the-art accelerators.

It is not a bad description of man to describe him as a tool making animal.

— Charles Babbage

Conclusion: RTMs have the potential to meet the multi-faceted requirements of next-generation computing systems. However, tools such as the ones presented in this thesis are needed to model RTMs and exploit their full potentials by explicitly optimizing for shift operations. Our results show that, in the best optimization scenario where RTMs need at most a single shift per access, they can outperform SRAM both in terms of energy consumption and performance.

This dissertation is based on the following journal and conference articles.

- [1] Robin Bläsing, Asif Ali Khan, Panagiotis Ch. Filippou, Chirag Garg, Fazal Hameed, Jeronimo Castrillon, and Stuart S. P. Parkin. "Magnetic Racetrack Memory: From Physics to the Cusp of Applications within a Decade." In: *Proceedings of the IEEE* 108.8 (Mar. 2020), pp. 1303–1321. DOI: 10.1109/JPROC.2020.2975719. URL: https://ieeexplore.ieee.org/document/9045991.

- [2] Asif Ali Khan, Norman A. Rink, Fazal Hameed, and Jeronimo Castrillon. "Optimizing Tensor Contractions for Embedded Devices with Racetrack Memory Scratch-Pads." In: *Proceedings of the 20th ACM SIGPLAN/SIGBED International Conference on Languages, Compilers, Tools and Theory of Embedded Systems (LCTES)*. LCTES 2019. Phoenix, AZ, USA: ACM, June 2019, pp. 5–18. ISBN: 978-1-4503-6724-0/19/06. DOI: 10.1145/3316482.3326351. URL: http://doi.acm.org/10.1145/3316482.3326351.

- [3] Asif Ali Khan, Fazal Hameed, Robin Bläsing, Stuart Parkin, and Jeronimo Castrillon. "RTSim: A Cycle-accurate Simulator for Racetrack Memories." In: *IEEE Computer Architecture Letters* 18.1 (Jan. 2019), pp. 43–46. ISSN: 1556-6056. DOI: 10.1109/LCA.2019.2899306. URL: https://ieeexplore.ieee.org/document/8642352.

- [4] Asif Ali Khan, Fazal Hameed, Robin Bläsing, Stuart S. P. Parkin, and Jeronimo Castrillon. "ShiftsReduce: Minimizing Shifts in Racetrack Memory 4.o." In: *ACM Trans. Archit. Code Optim.* 16.4 (2019). ISSN: 1544-3566. DOI: 10.1145/3372489. URL: https://doi.org/10.1145/3372489.

- [5] Asif Ali Khan, Andrés Goens, Fazal Hameed, and Jeronimo Castrillon. "Generalized Data Placement Strategies for Racetrack Memories." In: *Proceedings of the 2020 Design, Automation and Test in Europe Conference (DATE)*. DATE '20. Grenoble, France: IEEE, Mar. 2020, pp. 1502–1507. ISBN: 978-3-9819263-4-7. DOI: 10.23919/DATE48585.2020.9116245. URL: https://ieeexplore.ieee.org/document/9116245.

- [6] Asif Ali Khan, Hauke Mewes, Tobias Grosser, Torsten Hoefler, and Jeronimo Castrillon. "Polyhedral Compilation for Racetrack Memories." In: IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 39.11 (2020), pp. 3968–3980. DOI: 10.1109/TCAD.2020.3012266.

To get to know, to discover, to publish this is the destiny of a scientist. François Arago

- [7] Asif Ali Khan, Sebastien Ollivier, Stephen Longofono, Gerald Hempel, Jeronimo Castrillon, and Alex K Jones. "Brain-inspired Cognition in Next Generation Racetrack Memories." In: *arXiv* preprint arXiv:2111.02246 (2021).

- [8] Joonas Multanen, Asif Ali Khan, Pekka Jääskeläinen, Fazal Hameed, and Jeronimo Castrillon. "SHRIMP: Efficient Instruction Delivery with Domain Wall Memory." In: *Proceedings of the International Symposium on Low Power Electronics and Design*. ISLPED '19. Lausanne, Switzerland: ACM, July 2019, 6pp. DOI: 10.1109/ISLPED.2019.8824954. URL: https://ieeexplore.ieee.org/document/8824954.

Other publications that I have co-authored but are not part of this dissertation.

- [1] Christian Hakert, Asif Ali Khan, Kuan-Hsun Chen, Fazal Hameed, Jeronimo Castrillon, and Jian-Jia Chen. "BLOwing Trees to the Ground: Layout Optimization of Decision Trees on Racetrack Memory." In: *Proceedings of the 58th Annual Design Automation Conference (DAC'21)*. DAC '21. San Francisco, California: ACM, Dec. 2021.

- [2] Fazal Hameed, Asif Ali Khan, and Jeronimo Castrillon. "AL-PHA: A Novel Algorithm-Hardware Co-design for Accelerating DNA Seed Location Filtering." In: *IEEE Transactions on Emerging Topics in Computing* (2021), pp. 1–1. DOI: 10.1109/TETC.2021.3093840.

- [3] Fazal Hameed, Asif Ali Khan, and Jeronimo Castrillon. "Improving the Performance of Block-based DRAM Caches Via Tag-Data Decoupling." In: *IEEE Transactions on Computers* 70.11 (2021), pp. 1914–1927. DOI: 10.1109/TC.2020.3029615.

- [4] Asif Ali Khan, Fazal Hameed, and Jeronimo Castrillon. "NVMain Extension for Multi-Level Cache Systems." In: *Proceedings of the Rapido'18 Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools.* RAPIDO '18. Manchester, United Kingdom: Association for Computing Machinery, 2018. ISBN: 9781450364171. DOI: 10.1145/3180665.3180672. URL: https://doi.org/10.1145/3180665.3180672.

- [5] Asif Ali Khan, Norman Alexander Rink, Fazal Hameed, and Jeronimo Castrillon. "Optimizing Tensor Contractions for Embedded Devices with Racetrack and DRAM Memories." In: *ACM Transactions on Embedded Computing Systems* 19.6 (2020), 44:1–44:26. ISSN: 1539-9087. DOI: 10.1145/3396235. URL: https://doi.org/10.1145/3396235.

- [6] Asif Ali Khan, Sebastien Ollivier, Fazal Hameed, Jeronimo Castrillon, and Alex K. Jones. "DownShift: Tuning Shift Reduction with Reliability for Racetrack Memories." In: *IEEE Transactions on Computers (submitted)*. 2022.

- [7] Adam Siemieniuk, Lorenzo Chelini, Asif Ali Khan, Jeronimo Castrillon, Andi Drebes, Henk Corporaal, Tobias Grosser, and Martin Kong. "OCC: An Automated End-to-End Machine Learning Optimizing Compiler for Computing-In-Memory." In: *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (2021), pp. 1–1. DOI: 10.1109/TCAD.2021.3101464.

- [8] Fazal Hameed et al. "Performance and Energy-Efficient Design of STT-RAM Last-Level Cache." In: *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 26.6 (2018), pp. 1059–1072. ISSN: 1063-8210. DOI: 10.1109/TVLSI.2018.2804938.

No one who achieves success does so without acknowledging the help of others. The wise and confident acknowledge this help with gratitude.

Alfred North Whitehead

#### **ACKNOWLEDGMENTS**

First and foremost, I want to express my sincere gratitude and appreciation to my supervisor Prof. Jeronimo Castrillon for his continuous support, encouragement, and constructive critique in this entire journey. He took a *timid* me and transformed me into a confident, independent researcher who is willing to take on new challenges. He gave me complete freedom, and at the same time, pushed and challenged me to keep improving my research, presentation, and writing skills. Thank you, Jeronimo, for believing in me, introducing me to all our collaborators, giving me immediate and invaluable feedback, even on the weekends, for all your patience, light chats, Table Tennis moments, and everything. I am also honored to have Prof. Akash Kumar as my second adviser, and I am grateful to him for his valuable feedback on my status talk.

I would like to thank my dearest colleagues at the Chair for Compiler Construction for their support in technical and non-technical matters. Coming from an entirely different culture, it wouldn't have been easy for me to integrate here if I hadn't had all those wonderful people. I want to thank everyone for all the exciting lunch table discussions, technical talks, team events, and feedback on my research talks, posters, and research papers. Special thanks go to Christian Menard and Gerald Hempel for all their support in fixing technical issues and for understanding and writing my German letters, Nesrine Khouzami and Hasna Bouraoui for their help to teach me pieces of German and Arabic languages and for exchanges on our cultural similarities, Julian Robledo Mejía and Lars Schütze for the energizer Table Tennis breaks. I want to thank Robert Khasanov, Alexander Brauckmann, Karl Friebel, Galina Kozyreva, and Andrés Goens for the excellent work-related and otherwise discussions. I would also like to thank Conny Okuma for her support in administrative affairs.

Without the tremendous support of all the amazing people with whom I worked within and outside the group, this thesis wouldn't be possible, or at least wouldn't be in this shape. To start with, I would like to thank Fazal Hameed for his guidance and genuine support in the early days of my Ph.D. He invited me to Dresden as a guest researcher, persuaded me to stay here, and introduced me to the memory subsystem and the memory simulation frameworks. I

want to thank Stuart Parkin and Robin Bläsing from the Max Planck Institute Halle (Saale) for hosting us at their institute and for the many meetings, discussions, and joint works that helped improve my understanding of the racetrack memories. I also want to thank my other co-authors: my colleagues Norman A. Rink, Andrés Goens, and Gerald Hempel, Panagiotis Ch. Filippou, and Chirag Gargi from the IBM research Almaden, Joonas Multanen and Pekka Jääskeläinen from the Tampere University, Christian Hakert, Kuan-Hsun Chen and Jian-Jia Chen from TU Dortmund, Sebastien Ollivier, Stephen Longofono and Alex K. Jones from the University of Pittsburgh, Tobias Grosser from the University of Edinburgh and Torsten Hoefler from ETH Zurich, for all the great discussions and from whom I have learned a great deal. I would particularly like to thank Hauke Mewes, who worked with me towards his master's thesis and, all my students and teachers with whom I worked in the past and from whom I learned at every step. Thank you, everyone!

I would also like to thank the Higher Education Commission (HEC) of Pakistan for financing the initial phase of my Ph.D. via the German foreign exchange service (DAAD), and the German Research Foundation (DFG), and the Center for Advancing Electronics Dresden (cfaed) since then. I want to thank HiPEAC for funding my research stay at ETH Zurich and Torsten Hoefler and Tobias Grosser, who was then at ETH, for hosting me at SPCL ETH and giving me the opportunity to work with them. The visit proved delightful learning and life experience where I made new friends. It was SPCL where I met Lorenzo Chelini, an exchange student from TU Eindhoven, with whom I had many great conversations and ended up doing joint research work.

Finally, and most importantly, I want to thank my family and friends, without whom this dissertation would not be possible, and I would not be here today. I want to thank my parents for their unconditional love and unparallel support, motivation, and prayers, my wife for sharing this journey with me and bearing with me in these difficult years, my beloved sisters, nephews, nieces, cousins, and most of all, my brother. I especially want to thank my lovely kids, Ridhwan and Lena, for taking care of my mental health by successfully distracting me in distressing situations and reminding me of the beautiful life beyond the work and screens. I would also like to thank my friends Tanveer Ahmad, Jebran Khan, Amaad Khalil, Shakir Ullah, Kashif Ahmad, and many others for all the pleasant conversations we have had in these five years.

# CONTENTS

| 1                                              | INT              | RODUC          | CTION 1                                                   |

|------------------------------------------------|------------------|----------------|-----------------------------------------------------------|

|                                                | 1.1              | Beyor          | nd the walls: The landscape of emerging non-              |

|                                                |                  | volati         | le memory technologies 2                                  |

|                                                |                  | 1.1.1          | Phase change memory (PCM) 3                               |

|                                                |                  | 1.1.2          | Resistive RAM (ReRAM) 3                                   |

|                                                |                  | 1.1.3          | Ferroelectric RAM (FeRAM) 3                               |

|                                                |                  | 1.1.4          | Magnetic RAM (MRAM) 4                                     |

|                                                |                  | 1.1.5          | Racetrack memory (RTM) 4                                  |

|                                                |                  | 1.1.6          | Prospects 5                                               |

|                                                | 1.2              | Comp           | outation in (racetrack) memory 6                          |

|                                                | 1.3              | RTM c          | hallenges 7                                               |

|                                                |                  | 1.3.1          | The shifting problem 7                                    |

|                                                |                  | 1.3.2          | Lack of simulation tools 8                                |

|                                                |                  | 1.3.3          | 1                                                         |

|                                                |                  |                | RTM 9                                                     |

|                                                | 1.4              |                | em statement and overview 9                               |

|                                                |                  | 1.4.1          | Device physics and simulation 9                           |

|                                                |                  | 1.4.2          | 1                                                         |

|                                                |                  |                | Instruction placement 12                                  |

|                                                |                  |                | Optimizing compilers for RTMs 13                          |

|                                                |                  | 1.4.5          | Hyperdimensional computing in RTMs 13                     |

|                                                | 1.5              |                | rtation contributions and roadmap 14                      |

|                                                | 1.6              |                | contributions 16  NDING DEVICE PHYSICS AND SIMULATIONS 19 |

| 2 UNDERSTANDING DEVICE PHYSICS AND SIMULATIONS |                  |                |                                                           |

|                                                | 2.1              | _              | etic Racetrack Memories 19                                |

|                                                |                  | 2.1.1          |                                                           |

|                                                |                  |                | RTM preliminaries 21                                      |

|                                                |                  | 2.1.3          | •                                                         |

|                                                |                  | 2.1.4          |                                                           |

|                                                |                  | 2.1.5<br>2.1.6 |                                                           |

|                                                |                  |                | Outlook 44 Conclusions 49                                 |

|                                                | 2.2              | -              | n: A cycle-accurate simulator for racetrack memo-         |

|                                                | 2.2              | ries           | 49                                                        |

|                                                |                  |                | Introduction 50                                           |

|                                                |                  |                | RTSim overview 51                                         |

|                                                |                  |                | Case studies 55                                           |

|                                                |                  | _              | Conclusions 56                                            |

| 3                                              | SHI              | •              | VARE SCALARS AND INSTRUCTION PLACEMENT                    |

| J                                              | RACK MEMORIES 59 |                |                                                           |

|                                                | 3.1              |                | domain wall block cluster (DBC) data placement 59         |

|                                                | <i></i>          |                | Introduction 59                                           |

|                                                |                  | -              | → A                                                       |

|                    |                                            | 3.1.2  | Background and motivation 62                    |  |  |

|--------------------|--------------------------------------------|--------|-------------------------------------------------|--|--|

|                    |                                            | 3.1.3  |                                                 |  |  |

|                    |                                            |        | ming (ILP) formulation 66                       |  |  |

|                    |                                            | 3.1.4  | Approximate data placement 67                   |  |  |

|                    |                                            |        | Results and discussion 74                       |  |  |

|                    |                                            |        | Related work 81                                 |  |  |

|                    |                                            | _      | Conclusions 83                                  |  |  |

|                    | 3.2                                        | -      | ralized data placement strategies for racetrack |  |  |

|                    |                                            | memo   |                                                 |  |  |

|                    |                                            | 3.2.1  | Introduction 84                                 |  |  |

|                    |                                            | 3.2.2  | Background 85                                   |  |  |

|                    |                                            |        | Generalized data placement in RTM 87            |  |  |

|                    |                                            |        | Evaluation 91                                   |  |  |

|                    |                                            |        | Related work 94                                 |  |  |

|                    |                                            | 3.2.6  | Conclusions and outlook 95                      |  |  |

|                    | 3.3                                        | SHRII  | MP: Efficient Instruction Delivery with Domain  |  |  |

|                    |                                            | Wall N | Memory 95                                       |  |  |

|                    |                                            | 3.3.1  | Introduction 96                                 |  |  |

|                    |                                            | 3.3.2  | Domain wall memory 97                           |  |  |

|                    |                                            | 3.3.3  | The shift-reducing instruction memory placement |  |  |

|                    |                                            |        | (SHRIMP) approach 98                            |  |  |

|                    |                                            | 3.3.4  | Evaluation 103                                  |  |  |

|                    |                                            | 3.3.5  | Related work 107                                |  |  |

|                    |                                            | 3.3.6  | Conclusions 108                                 |  |  |

| 4                  | OPT                                        | IMIZIN | IG COMPILERS FOR RACETRACK MEMORIES 109         |  |  |

|                    | 4.1                                        | Tenso  | r contractions in RTMs 109                      |  |  |

|                    |                                            | 4.1.1  | Introduction 109                                |  |  |

|                    |                                            |        | Background 111                                  |  |  |

|                    |                                            | 4.1.3  | Data layout for minimal shifting 115            |  |  |

|                    |                                            |        | Evaluation 124                                  |  |  |

|                    |                                            | 4.1.5  | Related work 128                                |  |  |

|                    |                                            | 4.1.6  | Conclusions 131                                 |  |  |

|                    | 4.2                                        | Polyh  | edral Compilation for Racetrack Memories 131    |  |  |

|                    |                                            | •      | Introduction 132                                |  |  |

|                    |                                            | 4.2.2  | Background 133                                  |  |  |

|                    |                                            |        | Program transformations for RTMs 138            |  |  |

|                    |                                            |        | Results and discussion 146                      |  |  |

|                    |                                            |        | Related work 153                                |  |  |

|                    |                                            | 4.2.6  | Conclusions 154                                 |  |  |

| 5                  | BRA                                        | IN-INS | PIRED COGNITION IN NEXT GENERATION RACE-        |  |  |

| TRACK MEMORIES 155 |                                            |        | MORIES 155                                      |  |  |

|                    | 5.1 Hyperdimensional computing in RTMs 155 |        |                                                 |  |  |

|                    | _                                          |        | duction 156                                     |  |  |

|                    | 5.3                                        | Backg  |                                                 |  |  |

|                    |                                            |        | Hyperdimensional Computing 158                  |  |  |

|                    |                                            | 5.3.2  | Use Case: Language Recognition 160              |  |  |

|                    |                                            |        |                                                 |  |  |

```

Racetrack Memory

5.3.3

5.4 Enabling Computation in Racetrack Memory

Logical Operations in RTM

5.4.1

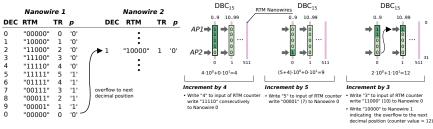

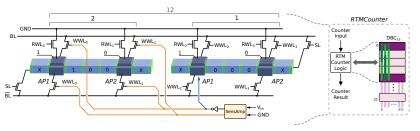

Counting in RTM

5.4.2

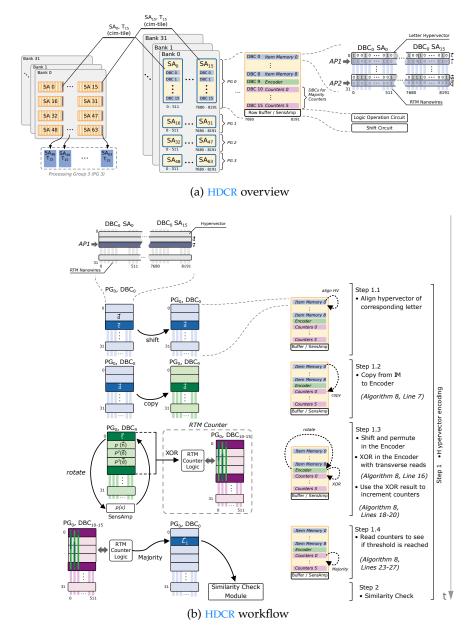

5.5 HyperDimensional Computing in Racetrack Memory

167

5.5.1

Overview

167

5.5.2

Item Memory

169

Encoding

5.5.3

171

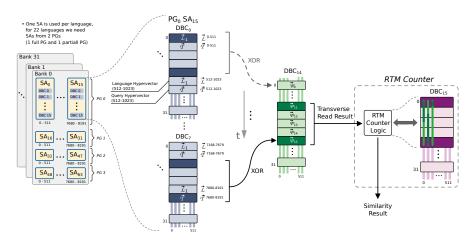

Inference

5.5.4

175

5.6 Evaluation

176

5.6.1

Experimental Setup

176

5.6.2 Data Set

177

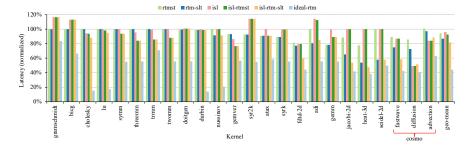

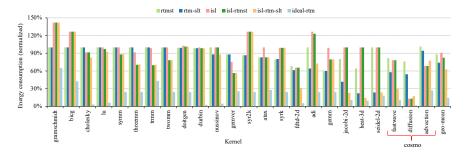

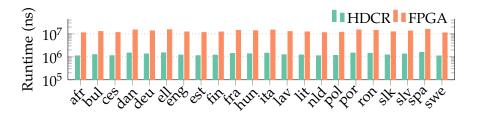

Performance Comparison

5.6.3

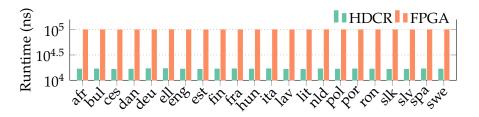

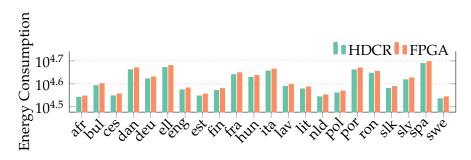

Energy Consumption

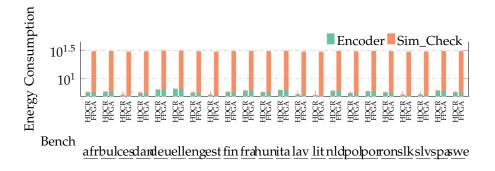

5.6.4

5.6.5

Comparison between HyperDimensional Comput-

ing in Racetrack (HDCR) and PCM

Related work

181

5.8 Conclusions

183

6 CONCLUSIONS AND OUTLOOK

185

6.1 Conclusions

185

6.2 Future work

186

BIBLIOGRAPHY

189

List of Figures

234

List of Tables

235

List of Listings

235

```

#### **ACRONYMS**

AP access port

AFD access frequency based distribution

AB alternation base

AC alternation candidate

AF antiferromagnetically

BB basic block

BLO bi-directional linear ordering

AM associative memory

CPU central processing unit

CTL chemical templating layers

CST chiral spin torque

CW clockwise

CIM computing in memory

CFG control flow graph

CNN convolutional neural network

CCW counterclockwise

DATE Design, Automation and Test in Europe

DMA disjoint memory accesses

DSL domain specific language

DW domain wall

DBC domain wall block cluster

DWM domain wall memory

DRAM dynamic random access memory

DMI Dzyaloshinskii-Moriya interaction

EC error correction

ECC error correction code

ED error detection

ECT exchange coupling torque

FeFET ferroelectric field effect transistor

FeRAM ferroelectric RAM

FPGA field-programmable gate array

FTJ ferroelectric tunnel junction

GA genetic algorithm

GEMM general matrix-matrix multiplication

GMR giant-magnetoresistance

GPU graphical processing unit

HW hardware

HDD hard disk drive

HDC hyperdimensional computing

HDCR HyperDimensional Computing in Racetrack

HV hypervector

IGA improved genetic algorithm

ILP integer linear programming

INLP integer nonlinear programming

IoT internet of things

ISLPED International Symposium on Low Power Electronics and Design

IM item memory

LR language recognition

LLC last level cache

LUT lookup table

MRAM magnetic RAM

MTJ magnetic tunnel junction

MM matrix multiplication

MWHP maximum weighted Hamiltonian path

MWHPC maximum weighted Hamiltonian path cover

MTTF mean time to failure

MRC multilane racetrack cache

MLC multi level cell

MLIR multi level intermediate representation

NPU neural processing unit

NDP near data processing

NMC near memory computing

NVM nonvolatile memory

OFU order of first use

OCC open CIM compiler

PTE page table entry

PCM phase change memory

PMA perpendicular magnetic anisotropy

PG processing group

PIM processing in memory

PC program counter

RTM racetrack memory

RM racetrack memory

RAM random access memory

RW random walk

RE rare earth

ReRAM resistive RAM

SPM scratchpad memory

SHRIMP shift-reducing instruction memory placement

SOA single offset assignment

SW software

SSD solid state drive

SOT spin-orbit torque

STT spin-transfer torque

# XX CONTENTS

SCoP static control part

SRAM static random access memory

STS sub threshold shift

SAF synthetic antiferromagnetic

TPU tensor processing unit

TACO Transactions on Architecture and Code Optimization

TM transition metal

TR transverse read

TRD transverse read distance

TMR tunneling magnetoresistance

VT Varshamov-Tenengolts

V-NAND vertical NAND

INTRODUCTION

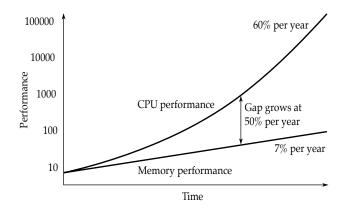

The memory system plays a defining role in computing systems' performance and energy consumption. However, this was not clear until the early 90's when scientists at NASA and UVa, while running highly-optimized hand-coded kernels, found them performing orders of magnitude slower compared to the peak performance [186]. They found the imbalance between processor and memory speeds as the main reason and named it the *memory wall* problem. The gap between the memory and processor speeds has continued and is expected to grow by around 50% per year (see Figure 1.1). Decades down the road, the mainstream computer architecture community still struggles to roll over it.

The massive rise of data generation due to mobile-connected devices and application domains such as computational bioinformatics and machine learning have further exposed the disparity in memory and computing capabilities of today's machines [252]. The larger memory footprint of these and other emerging application domains demands higher memory capacities. However, increasing the capacity of traditional SRAM and dynamic random access memory (DRAM) technologies is barred by various factors, including the technological scaling of the device, wireability of the silicon interposers, the technological limit on the number of memory stacks, and the amount of chip pinouts [24, 143]. This leads to the memory capacity wall. The die-stacking of memory layers in DRAM has partially alleviated the problem by increasing the capacity; however, it also increases the overall energy consumption of the memory system. The refresh frequency in die-stacked DRAM needs to be at least doubled in order to maintain its data [329], increasing the refresh power to as high as 47% of the total power consumption of a 64 Gbit DRAM device [264]. This strengthens the power wall and exacerbates the memory system's overall power consumption, which already dominates the system power consumption and contributes to it by as much as 46% [70].

In addition to the speed, capacity, and power challenges, data movement in conventional von-Neumann machines also consumes a considerable amount of the system's energy. For a floating-point operation, the data movement between the *central processing unit* (CPU) and the off-chip memory consumes two orders of magnitude more energy compared to the operation itself [161], a problem that can not be solved by simply scaling the memory devices or improving their speed. To alleviate this problem, recent research advocates bringing computations closer to the memory and processing data where it

Figure 1.1: The memory wall problem. For over four decades, the gap between processor and memory speeds has increased by around 50% per year [226]. Today, in some architectures, this gap has widened to as high as  $1000 \times [212]$ .

makes more sense. This has led to the development of a number of memory-centric architectures, including the Google tensor processing unit (TPU) [110], Microsoft Brainware neural processing unit (NPU) [348], NVIDIA'S V100 [358], DianNao series of chips [366] and many others [339]. These accelerators are orders of magnitude faster and energy-efficient compared to von-Neumann machines. However, these solutions are domain-specific and employ conventional DRAMs with known scaling and power limitations.

In the remainder of this chapter, we present an overview of the prominent NVM technologies and their prospects in future computing systems. We particularly focus on RTMs and discuss their strengths and associated challenges. Finally, we discuss how this thesis addresses some of those challenges to improve RTM performance and energy consumption.

# 1.1 BEYOND THE WALLS: THE LANDSCAPE OF EMERGING NON-VOLATILE MEMORY TECHNOLOGIES

The conflicting demands for higher capacity, better speed, and reduced energy consumption of memory devices have led to the emergence of several NVM technologies. Today, NVM technologies can be found in systems ranging from IoT sensor nodes to mobile devices and personal computers to high-performance computing servers. The tremendous market growth of these technologies (an anticipated CAGR of 10.26% during 2022-2027) is made possible simultaneously by the end of Moore's law and their potential to increase the system's functionality. Most of these NVM technologies can potentially operate in the *picosecond* timescale, making them thousands of times faster compared to the *nanosecond* timescale conventional technologies [324]. The nonvolatility of these emerging NVMs also makes them highly energy-efficient.

In the following, we present a brief overview and working principle of the most promising emerging NVM technologies, primarily focusing on their device endurance, cell sizes, access latencies, and energy consumption.

#### 1.1.1 Phase change memory (PCM)

PCM is a resistive memory technology that uses reversible phase changes in materials to store information. The first prototype of a 256 bits PCM was demonstrated in 1970 [208]. Today, it is probably the most widely studied NVM technology. A PCM device consists of a phase-changing material that changes states between crystalline (a low resistance state) and amorphous (a high resistance state) and is sandwiched between two electrodes. The two resistance states of the material represent two logic states, i.e., a binary 1 and 0. PCM, generally, requires a high programming current (> 200  $\mu$ A) but this can be reduced to < 10  $\mu$ A by scaling down the device itself [27, 310]. Since the PCM device stores information in the form of resistance, it can be programmed to more than two resistance states (multi-level cells) to represent more than a single bit. This, however, can not be relied upon in the long run as the device resistance drifts over time, making it difficult to differentiate between resistance states.

#### 1.1.2 Resistive RAM (ReRAM)

ReRAM is another class of resistive memory technologies that use resistive switching phenomenon in metal oxide materials to store information [309]. A cell in ReRAM consists of a top and a bottom electrode and a thin oxide layer in between. For resistive switching, a high electric field is applied to the ReRAM cell, which generates oxygen vacancies in the metal oxide layer. This leads to the formation of conductive filaments and changes the device state from high resistance to a low resistance (set) state. For switching back to the high resistance (reset) state,  $V_{RESET}$  is applied to the device to break the conductive filament and allow the oxygen ions to migrate back to the bulk. ReRAM, compared to PCM, has higher write endurance (>  $10^{10}$ ), faster write operations, larger resistance on-off ratios, and better scalability prospects [309]. However, it suffers from inconsistent electrical characteristics, i.e., larger variations in resistance across devices [310].

#### 1.1.3 Ferroelectric RAM (FeRAM)

FeRAM stores information in ferroelectric capacitors, devices that consist of ferroelectric materials interposed between two metallic electrodes [259]. An electric field's application across the ferroelectric material changes its polarization, which the device retains even if

4

the electric field is removed. The polarization state of the device thus represents logic stats and is used to store information. Overall, Feram, compared to most NVM technologies, has better endurance (  $10^{14}$ ). However, it suffers from larger cell size, which, when scaled down, leads to a smaller/undetectable amount of charge storage [122]. Further, it also suffers from destructive read operations. The latest research in ferroelectric memories broadens the scope of exploration of ferroelectric materials and is investigating them with *ferroelectric field effect transistor* (FeFET) [95], and *ferroelectric tunnel junctions* (FTJs) [67].

# 1.1.4 Magnetic RAM (MRAM)

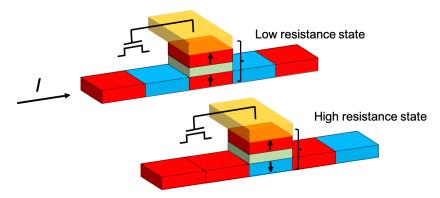

MRAM stores information in nanometric scale ferromagnetic elements in the form of their magnetic orientation [66]. A cell in MRAM consists of two ferromagnetic layers, a fixed reference layer and a free layer, separated by an insulating layer. The free layer in the MRAM cell stores the actual data bit, and its orientation can be changed/written using various techniques. The most common one among them is the spin-transfer torque (STT-MRAM) that employs spin-polarized electric current to change the free layer's magnetic orientation. The relative orientations of the free and fixed layers have different resistance states associated with them. In order to read/sense data from an MRAM cell, an electric current is passed through the cell, and the resistance of the device is measured. MRAM has virtually unlimited endurance and acceptable access latency. However, it suffers from a larger cell size and smaller on-off resistance ratio [122]. The latter makes it impossible for an MRAM cell to store more than one bit.

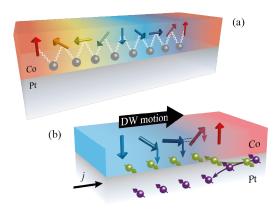

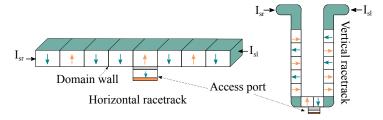

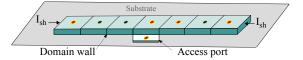

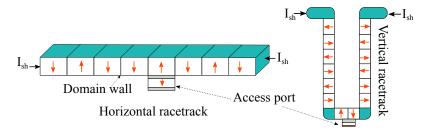

#### 1.1.5 Racetrack memory (RTM)

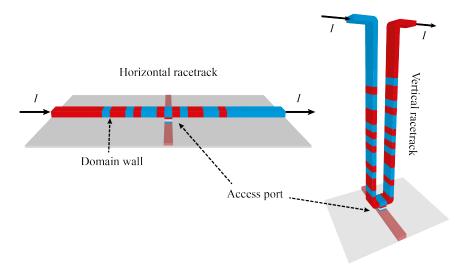

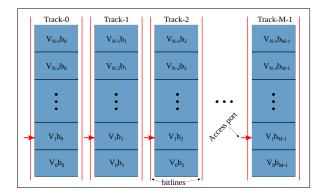

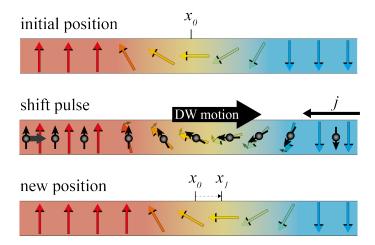

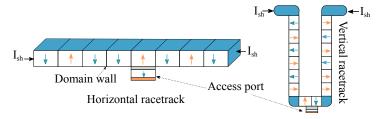

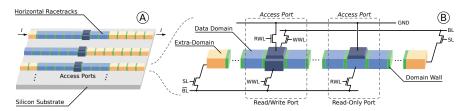

Compared to all other NVMs, RTM is relatively new and was originally proposed in 2008 [221]. Similar to MRAM, it also stores information in the form of the magnetic orientation of the magnetic material. However, unlike MRAM, a single cell in RTM is a magnetic nanowire that is further split into tiny magnetic regions. These regions range from a few 10s to a few 10os and are referred to as *domains* (in *domain wall memory* (DWM)) or *skyrmion* (in skyrmions based RTMs). Each domain (skyrmion) in the nanowire has its own magnetization direction (topological order) and represents a data bit. In addition, each nanowire is associated with one or more *access ports* (APs) that allow accessing data bits in the nanowire. Due to the larger footprint of the access transistor in the APs, the number of ports per track in RTM is generally smaller than the number of data bits. This makes RTM cells innately sequential, unlike any other NVM, and necessitates data to be moved to the port position before it can be accessed. From the performance perspective,

RTM promises to be as fast as SRAM, with the device having unlimited endurance.

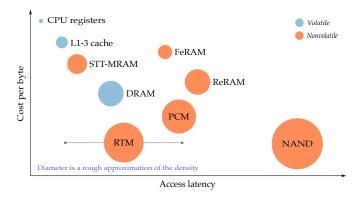

Figure 1.2: Performance and density comparison of emerging and conventional memory technologies [51].

#### 1.1.6 Prospects

Emerging NVM technologies offer potential solutions to the memory, capacity, and power walls but at the same time bring their own unique set of challenges. Figure 1.2 compares the above-mentioned NVMs to the conventional SRAM and DRAM technologies in terms of performance, density, and cost per byte. A more detailed comparison of these technologies is presented in Table 2.1 and Table 3.1. Presently, there is no clear winner, and non of the available technologies have the potential to become a *universal* memory. Phase change memories are relatively more established and have already been employed to bridge the wide gap between memory and storage. The low latency and byte-addressability of PCM allow using it as a DRAM extension, as a stand-alone storage device or as a persistent memory [82]. However, it suffers from limited write endurance and requires higher energy access time for the write operations. FeRAM devices exhibit incredible insensitivity to radiations and are deemed ideal for aerospace applications. However, their larger cell sizes constrain higher capacities. ReRAM is considered as an ideal candidate to replace NAND flash, but it also suffers from higher variability and limited write endurance [51]. MRAM has smaller access latencies and better write endurance, but its larger cell size restricts its applicability to systems having only limited memory capacity requirements. MRAM and FeRAM are also commercially available but only in smaller (MB) capacity ranges.

Racetrack memories promise to offer at least an order of magnitude higher capacity compared to other technologies, SRAM/DRAM comparable best-case latency, lower per-byte cost, and higher durability. In addition, they exhibit unique physical properties that enable *in-place* computations (see 1.2). However, unlike all other NVMs, RTMs pose a unique challenge in their sequentiality. The *shift operations* — required

to move data to access ports — not only lead to variable access latencies but also incur latency and energy penalties, as the time and energy required to access a bit in a nanowire depend on its position relative to the access port. Nonetheless, since none of the existing technologies satisfy the multi-faceted requirements of today's systems, next-generation technologies such as RTMs deserve to be investigated in detail. In the scope of this dissertation, we explore the RTM device characteristics and architectures in detail and study mechanisms to make them viable for software optimizations. We present simulation and compilation tools that exploit RTMs to their full potential and mitigate their limitations.

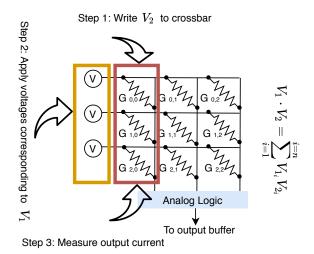

#### 1.2 COMPUTATION IN (RACETRACK) MEMORY

The next leap forward in energy-efficient computing is anticipated in non-von-Neumann system models such as near memory computing (NMC), also known as near data processing (NDP), or computing in memory (CIM). In the CIM paradigm, the physical attributes of the memory devices are exploited to implement logic and compute operations in-place. Resistive technologies, e.g., PCM and ReRAM, have attracted significant interest due to their ability to perform vector-vector and matrix-vector (MV) like operations in constant time [260]. To explain how they implement these operations, consider two fixed-size vectors  $V_1$  and  $V_2$  and the crossbar configuration of memory devices as shown in Figure 1.3. Initially, the memory devices in the first column (red box) are programmed to conductance values corresponding to  $V_2$ . Subsequently, the input voltage corresponding to V1 values is applied to all rows (yellow box). The measured current of the entire column is an approximation of the dot product of the two vectors (see Figure 1.3). The same basic physics principles are exploited to accelerate applications from machine learning and other domains [43, 269, 338, 340].

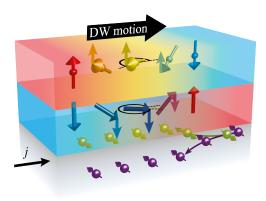

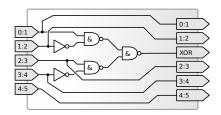

For RTMs, researchers have exploited the resistance states associated with the magnetic orientation of domains to implement in-place operations. For instance, Wang et al. exploited the *giant-magnetoresistance* (GMR) effect to realize an RTM-based XOR gate [301]. The same idea was later extended to implement other logic and compute operations [5, 6, 100]. Luo et al. fabricated reconfigurable NAND and NOR logic gates that perform operations using the current-induced domain wall motion [172]. The NAND gates are then used to implement XOR and other full-adder operations. Of late, a number of domain-wall-based [246, 267] and skyrmions-based [170, 322] in-RTM computing devices have been presented and used for various applications [335].

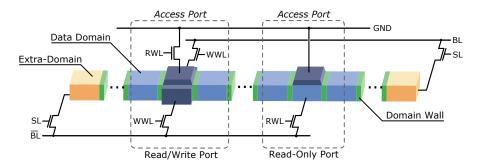

Recently, an alternate access mechanism called *transverse read* (TR) was proposed that reports the number of 1's (or o's) in the nanowire [350]. By applying a sub-shift-threshold current at an access port or an ex-

tremity of the nanowire (see Figure 1.4), and performing a normal read operation at the nearest access port, it is possible to detect how many domains are in a certain magnetic orientation between those two points. The TR operation has the potential to implement various logic and compute operations [359]. However, they are not thoroughly explored as of today.

Figure 1.3: Mapping a dot product to the CIM crossbar [268].

Figure 1.4: Anotomy of the RTM nanowire.

#### 1.3 RTM CHALLENGES

Despite their promising characteristics and significant performance and energy gains in isolated use cases, RTMs face multiple challenges that need careful consideration for the technology to go mainstream<sup>1</sup>.

#### 1.3.1 The shifting problem

From an architectural standpoint, shifting in RTM is *the* major challenge that brings latency, energy, and reliability penalties. In the worst-case

<sup>1</sup> Note that the challenges discussed in this section do not include fabrication related issues that require special attention, particularly in 3D RTMs.

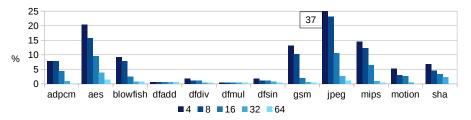

shifting scenario, the RTM access latency can be up to  $25.6 \times$  higher than the SRAM [356] latency, while for certain workloads, in the ideal-case maximum one shift per access, RTM can outperform SRAM by 24% [124]. They also take around 50% of the RTM energy [342]. In addition to the latency and energy overheads, the shift operations can also induce position errors, i.e., where at the end of the shift operations, the data bits in the nanowire are not aligned to the desired port positions [325]. The typical position error rate in an RTM cell is  $10^{-4} - 10^{-5}$ . A rich body of research is dedicated to explore and mitigate these errors [34, 35, 96, 183, 211, 285, 316, 326].

Minimizing the number of shift operations in RTM not only alleviates the latency and energy overheads but also indirectly reduces the number of position errors. A number of optimization techniques exist that aim at minimizing the amount of RTM shifts. Broadly, they can be categorized into two classes, i.e., hardware-based solutions and software-based solutions. Hardware-based techniques employ additional hardware, e.g., monitors or predictors, to monitor hot memory blocks and map them to RTM locations closer to access ports [277] or predict the next access location and proactively align data to access ports [47]. Similarly, novel memory controllers are proposed to reorder memory accesses by prioritizing requests accessing addresses closer to the access port [181]. While most of these techniques effectively mitigate or hide the shift operation latency, they do not guarantee a reduction in energy consumption. These solutions also employ additional hardware, bringing small but non-negligible latency, energy, and area overheads. On the contrary, software-based solutions such as shift-aware data placement [42, 180, 315] and compiler-assisted schedule and layout transformations can significantly reduce the number of shift operations with little to no overheads.

#### 1.3.2 *Lack of simulation tools*

The development of simulation tools for novel technologies such as RTMs is imperative. It is critical to explore and evaluate them across the memory stack. Particularly, it is essential to investigate and assess their feasibility in the memory subsystem and their suitability for different application domains. Multiple design alternatives of a memory system may exist that satisfy the user and application requirements. To explore these design alternatives in RTM-based systems and investigate different perspectives, new simulation tools are needed that model RTM-specific design parameters. In the literature, people have reported modifications to existing simulators such as gem5 [168], simplescalar [11] and NVMain [233] for exploring RTMs at various hierarchy levels in the memory subsystem [327, 355]. However, these extensions are not available publicly, which not only deprives the memory research community of exploring RTMs but also makes it near

to impossible to compare results, a process that is key for advancing the field.

# 1.3.3 The unfathomed potential of computation-in-RTM

Section 1.2 presents several techniques highlighting RTM's potential in CIM systems. In the majority of these solutions, the GMR effect is exploited, which, from the CIM perspective, does not give any competitive edge to RTMs compared to resistive technologies. The relatively newer TR operations have the potential to perform multi-operand operations in a single read, making RTM an ideal fit for bulk bitwise operations. However, the TR operations are underexplored. Ollivier et al. explain how these operations can be used to implement various logic and compute operations [359]. By the time of writing this dissertation, no other research exists that harnesses the potential of TR operations to accelerate an entire application or investigates their potential to implement other operations.

#### 1.4 PROBLEM STATEMENT AND OVERVIEW

The goal of this dissertation is to address the major RTM challenges discussed in Section 1.3 by understanding the RTM device characteristics and system behavior through rigorous experimentation and designing custom solutions. For RTM-based CIM systems, we aim to benefit from the device knowledge to map compute-primitives to RTM and improve the throughput and energy efficiency. For shifts minimization, we investigate the potential of higher (compiler) abstraction to analyze the memory access behavior of applications and design solutions that reorder memory accesses or assign temporaly closely accessed memory objects to spatially closed RTM locations.

To achieve this, we investigate the following research lines.

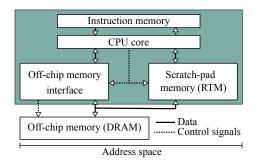

## 1.4.1 Device physics and simulation

For RTMs, different design alternatives may include different positions in the memory hierarchy. This can also be domain/application dependent. For instance, some applications may benefit more from RTM when used as on-chip memory, while others, with a limited locality, may exploit it to its full potential as an off-chip memory. Similarly, for the device itself, the selection of magnetic material, device structure, sensing element, and curvature enable numerous tradeoffs, including the controlled movement of domains, the critical current densities, and the RTM density. In this thesis, we survey the entire landscape of the physical developments in RTMs and their application in the memory hierarchy.

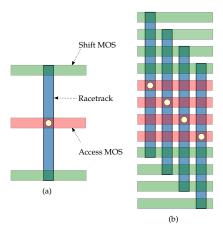

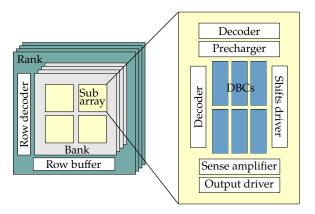

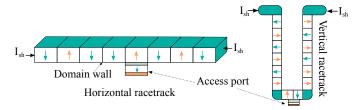

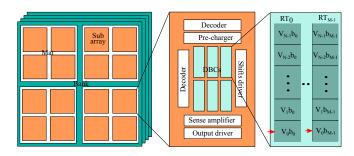

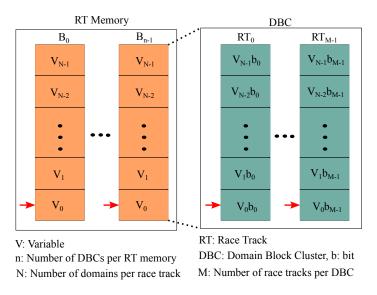

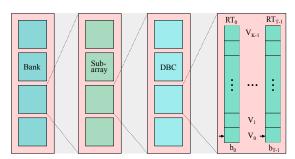

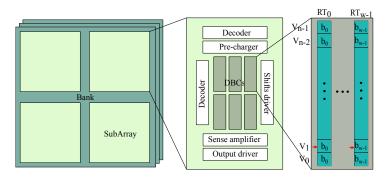

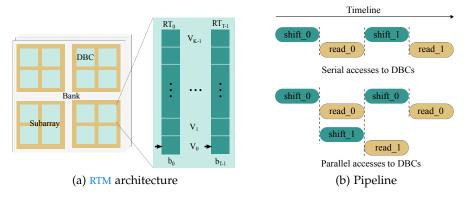

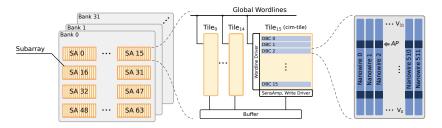

Similarly, like conventional memory technologies, RTMs are organized into mats, arrays, banks, and ranks. However, they also have their unique set of parameters, such as the following, that may enable different tradeoffs and, therefore, need careful consideration in the system design.

- Bits per cell: The size of the nanowire, i.e., the number of bits per cell, can be configured and is probably one of the most important design parameters of RTM. While the nanowire's actual length is fixed, the number of bits per cell can be varied. This parameter may have a direct impact on the number of shifts per access, the number of *overflow bits*<sup>2</sup>, the shift current density, and the RTM reliability.

- Access port types: An access port in RTM can either be a readwrite port or a read-/write-only port. The implications of the design choice of the AP types may not be self-evident. Still, they may affect the memory controller's design complexity and optimizations at the compiler and architectural level.

- Number of ports per cell: The number of access ports per cell directly impacts the RTM latency, regardless of the cell size and access port types. The tradeoff is between the access latency and the area overhead.

- Access ports management: Associating access ports to the data bits in a nanowire is also a design parameter that can potentially affect the memory controller's complexity and the RTM access latency.

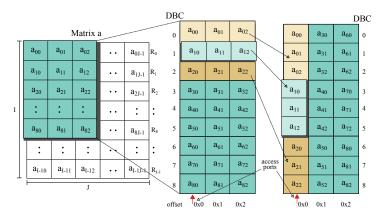

- DBC size: In RTMs, cells are grouped together to form *domain wall block clusters* (DBCs). All nanowires in a DBC are moved together and can be accessed in parallel. The DBC size will potentially impact the shift current density as well as simultaneous access to different regions of the memory. This may also directly impact the overall energy consumption; since the tracks in a DBC are moved in a lock-step fashion, not all data bits may be required at a certain time.

We study and understand these parameters in detail before developing an architectural simulation tool that can accurately model RTM-based systems.

#### 1.4.2 Data placement in RTM

Compiler-guided data placement is one of the known and effective optimization techniques that has already been used in optimizations

<sup>2</sup> Overflow bits are the additional bits at both ends of the nanowire to avoid data loss during the shift operations.

for other conventional and emerging memories [159, 227, 261, 305]. The idea is to map data objects to memory locations in a way that maximizes data locality and improves the system's performance. For NVMs with limited write endurance, data placement is used to intelligently handle the expensive write operations and improve the system lifetime and performance.

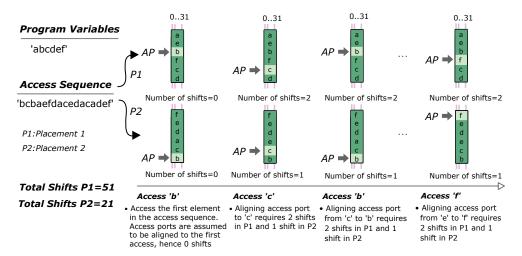

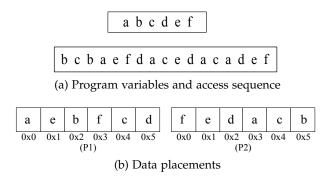

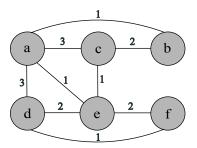

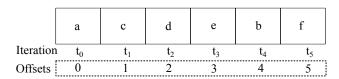

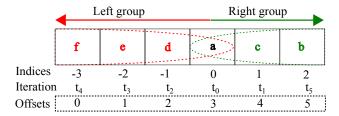

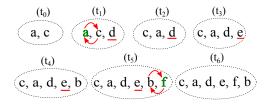

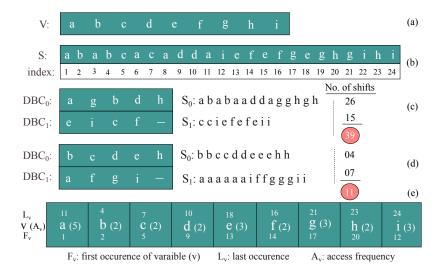

For shifts minimization in RTMs, we also see great potential in data placement solutions. Let us consider a toy example to highlight this. Assume a program has 6 data items, and they are accessed in the order shown in Figure 1.5 (access sequence on the left). We refer to the set of program data items as the set of *program variables* ( $\mathcal{V}$ ) and the set of their access order as *access sequence* or *program (memory) trace)* (S), where  $S_i \in \mathcal{V} \ \forall i \in \{0,1,\ldots,|S|-1\}$ , for any given source code.

As a target system, let us initially assume a simplistic RTM architecture having a single DBC. We assume that each track in the DBC has a single read/write port and the size of the data items matches the DBC word size, i.e., the number of tracks in the DBC. Let us further assume that the access ports in the DBC are aligned to the position of the first data item in the access sequence (b in this case).

With these assumptions, let us take two different memory placements of the program variables, a randomly chosen naive placement (P1) and a more carefully selected placement (P2), as shown in Figure 1.5.

Figure 1.5: Data placement impact on the RTM shifts. An intelligent placement, P2 in this case, can reduce the number of shifts by more than 2× compared to a naive placement, P1 in this case.

The total number of shifts for the two different placements, P<sub>1</sub> and P<sub>2</sub>, are shown in Figure 1.5. The absolute difference of the memory offsets of successive accesses is accumulated to compute the shift cost. For instance, for the given access sequence and the placement P<sub>1</sub> in the figure, access to the first variable b does not require any shifts since we assume that access ports are aligned to this position. For

accessing c, two shifts are required to align it to the port position (shift cost = 2). Similarly, for the next access, i.e., b, two shifts are required again, making the total shift cost equal to 4. The same is repeated for the entire access sequence to get the total shift cost for a particular placement.

The total shift cost in the naive data placement P1 amounts to 51 in accessing the entire access sequence, while P2 incurs only 21. Even for this tiny example, the shift cost is reduced by around  $2.4\times$ .

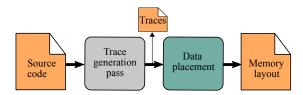

To compute efficient mappings, such as P2 in this example, we design heuristic solutions that take the memory trace as input and analyze it for access frequency and locality of the memory objects. Based on this information, memory objects that are frequently accessed with each other are mapped to successive or nearby locations in RTM.

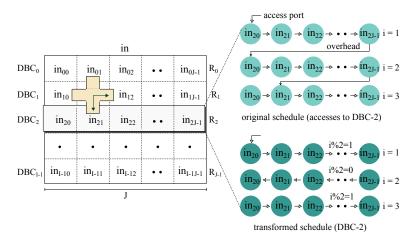

# Inter-DBC data placement

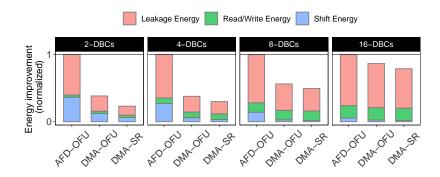

The data placement problem becomes more interesting and challenging if we consider more realistic and generic multi-DBC RTM architectures. The shift cost in such systems not only depends on the exact offset of memory objects within DBCs but also on their distribution across DBCs. Let us name these two problems as *intra-DBC* and *inter-DBC* data placement problems, respectively. A randomly chosen distribution of memory objects across DBCs can considerably increase the amount of RTM shifts. Even for a smaller memory trace such as Figure 3.20-(b), the carefully chosen inter-DBC placement Figure 3.20-(d) reduces the number of RTM shifts by more than 3.5× compared to the random distribution in Figure 3.20-(c).

We develop a heuristic solution that, similar to intra-DBC solutions, inputs a memory trace and analyses it for the memory objects' access frequency and liveliness. Based on the liveliness analysis, the algorithm identifies memory accesses with disjoint lifespans and assigns them to separate DBCs. For a single run of an application, accesses to these DBCs always incur at most one shift. For all other DBCs (storing non-disjoint memory objects), we apply intra-DBC optimizations to find efficient mappings.

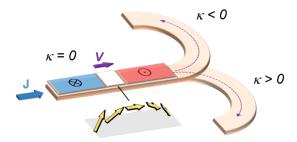

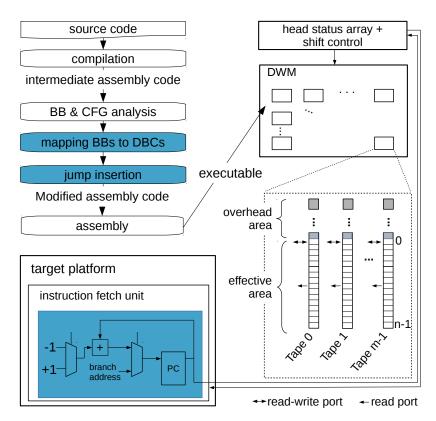

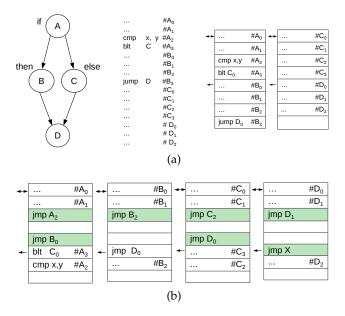

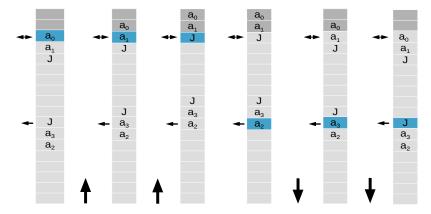

#### 1.4.3 Instruction placement

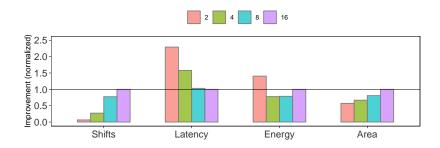

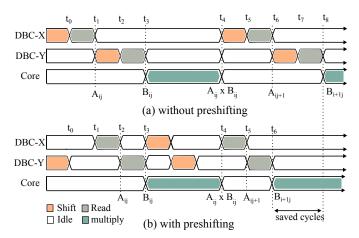

Instruction streams, unlike scalar accesses, are more sequential and have better compile-time analyzable patterns. Intuitively, this makes RTM an ideal choice for instruction memory. However, in repetitive control structures (loops), the instructions in the loop are accessed more than once. If employed naively, RTM-based instruction memory can lead to potential execution stalls as the access ports at the beginning of each new iteration needs to be reset to the first loop instruction. To avoid these long shifts and potential execution stalling, we, in

collaboration with Tampere University, propose a novel RTM-specific instruction placement method that ensures a maximum of one shift per each new instruction access.

# 1.4.4 Optimizing compilers for RTMs

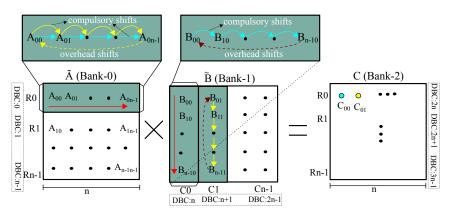

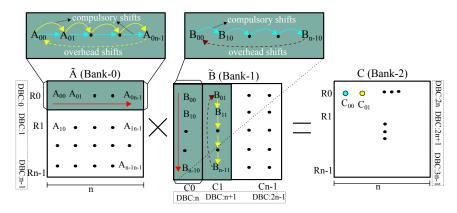

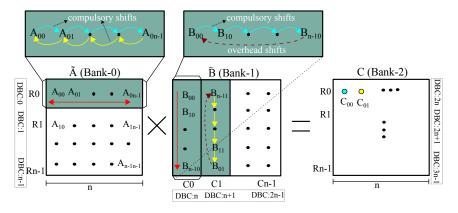

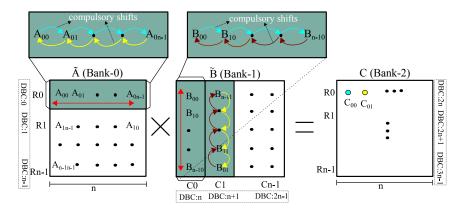

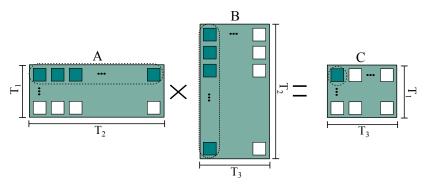

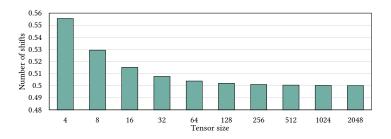

Section 1.4.2 and Section 1.4.3 motivated the need of optimization techniques for scalar accesses (simplified single-DBC architectures and generic multi-DBC architectures) and instruction streams. Let us now look into potential optimization opportunities for array access in RTMs. Consider the *general matrix-matrix multiplication* (GEMM) example in Figure 1.6 where each matrix is assigned to a separate bank and each DBC in a bank stores a matrix row (for matrices  $\tilde{A}$  and  $\tilde{C}$ ) or a matrix column ( $\tilde{B}$ ). Assume that access ports in all DBCs are initially pointing to the first location. Since the rows and columns of matrices  $\tilde{A}$  and  $\tilde{B}$ , respectively, are accessed more than once, each new value of C requires the access ports in DBCs to be aligned to the first element, incurring very long *overhead* shifts. These overhead shifts make roughly 50% of the overall RTM shifts.

Figure 1.6: GEMM with a naive memory layout

To eliminate the long overhead shifts in GEMM like kernels, we explore schedule and layout transformations that enable accessing RTM DBCs in a zig-zagging fashion. Similar to the data placement generalization in the previous section, we subsequently develop more generic transformations that are domain-independent and optimize for applications with repetitive accesses to array locations.

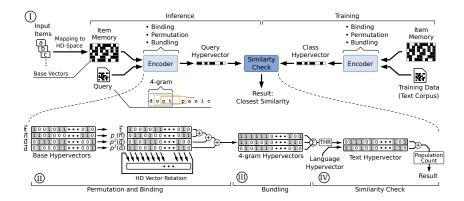

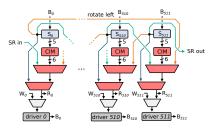

#### 1.4.5 Hyperdimensional computing in RTMs

To explore the transverse read operation in detail and the RTM CIM potential compared to resistive memory technologies, we accelerate an entire *hyperdimensional computing* (HDC) framework in RTM. The use case consists of operations such as XOR, majority, rotate operation,

and bit counting, which we plan to implement in RTM using the RTM device characteristics.

This is a cumulative dissertation combining several articles published in peer-reviewed conferences and journals. Each chapter consists of one or more research articles which is why some figures may appear more than once in the same chapter, and some text may be redundant (mainly text and figures on the RTM device and architectures). At the beginning of each chapter, we include an introductory paragraph that provides a high-level overview of the chapter and refers to the published articles. A small paragraph towards the end of each chapter reflects on the subjects discussed and makes a connection to the following chapter.

#### 1.5 DISSERTATION CONTRIBUTIONS AND ROADMAP

This thesis makes multi-fold contributions. It reviews the RTM evolution from its inception to its applications in the memory hierarchy and otherwise. From the architecture and programmability perspectives, it identifies the major challenges and proposes optimizations to address them.

Concretely, the following contributions are made.

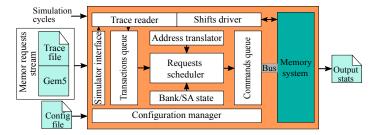

- 1. We review RTM's major breakthroughs and developments to understand its device physics, working principle, and overall architecture. We use this knowledge and develop an open-source RTM simulation tool RTSim that accurately models RTM, its shifting operation, and the port access and management policies (Chapter 2). This is based on [22, 125].

- 1.1. We present a thorough overview of the prominent RTM applications in the memory subsystem (Section 2.1.4), including its hardware/software optimizations, shifts minimizations techniques, and RTM misalignment correction schemes (Section 2.1.5).

- 1.2. The thesis also presents an overview of the critical technology parameters, i.e., threshold current densities and their impact on the movement speed of domain walls, the impact of various materials on domain wall motion, and novel domain wall driving mechanism (Section 2.1.3).

- 1.3. Our simulation tool, RTSim, is built on top of the NVMain simulator [234] which is fully configurable and facilitates the integration of new modules, such as the position error correction. For a full system simulation, RTSim can be patched to the gem5 [20] full system simulator, enabling exploration for different optimization objectives (Section 2.2).

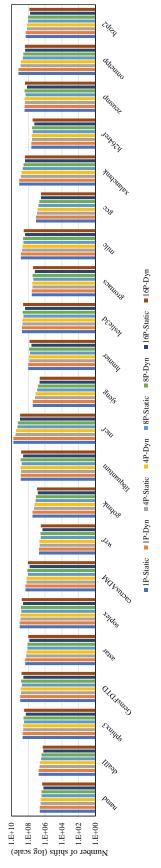

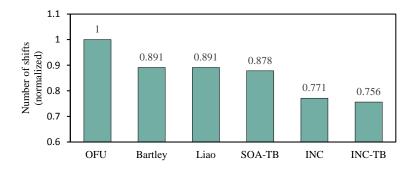

- 2. We propose novel optimization heuristics for scalars and instruction placements in RTM that minimize the number of shifts (Chapter 3). This is based on [126, 127, 203].

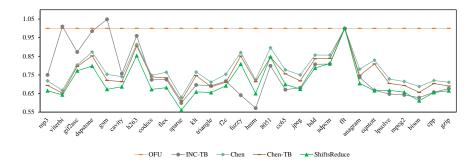

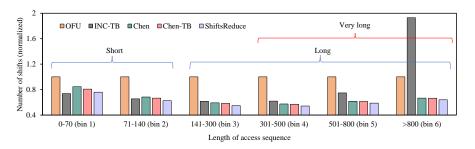

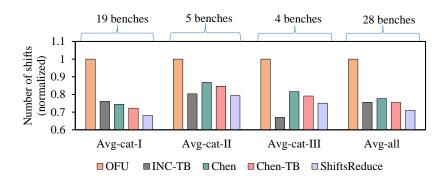

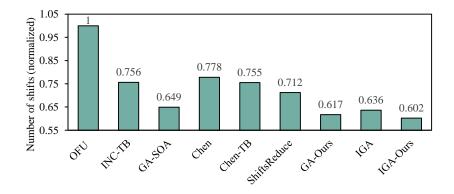

- 2.1. For data placement in a single DBC, we reconsider a set of data placement heuristics that were originally proposed for objects placement in DSP stacks. We develop a novel heuristic, ShiftsReduce, that analyzes the memory trace to construct an adjacency graph and computes memory offsets such that frequently accessed memory objects are placed in nearby RTM locations. An ILP formulation of the problem is developed to find the optimal placement and quantify the difference in the heuristics performance and the optimal one (Section 3.1).

- 2.2. For generic multi-DBC RTM architectures, we present a novel heuristic that analyzes the memory trace for objects with disjoint lifespans and steers disjoint and non-disjoint memory objects to separate DBCs. This separation significantly improves the temporal locality of the memory objects. We also develop a heuristic based on genetic algorithms that achieve near-optimal results (Section 3.2).

- 2.3. For RTM as an instruction memory, we consider two access ports per nanowire. We design a heuristic that extracts the repeatedly accessed *basic blocks* (BBs) from an input application, splits each BB into two halves, aligns the first half to the first access port in each DBC, and the second half *in reverse* to the second port. With this mapping, when the first access port finishes accessing the first half of the BB, the second access port is automatically aligned to the first instruction in the second half of the basic block (Section 3.3).

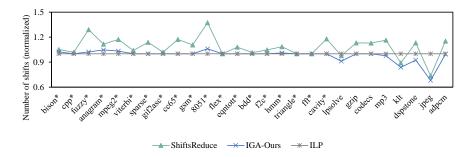

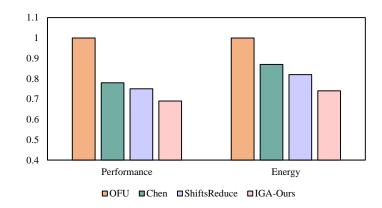

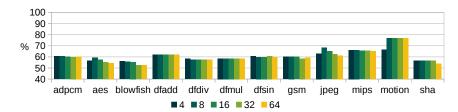

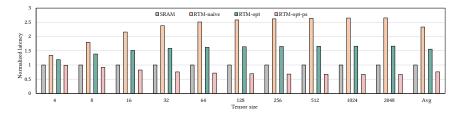

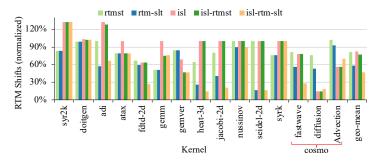

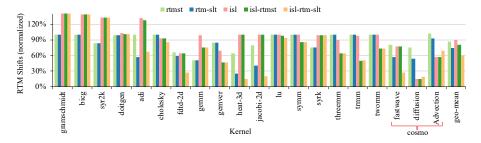

- 3. In domains such as machine learning, where kernels are well-structured and well-understood, compiler transformations are proposed to achieve ideal-RTM equivalent performance. An ideal RTM requires at most one shift for each memory access. An automatic compilation framework is developed that analyses an input application if it has any potential for RTM optimizations and applies loop/layout transformations to generate RTM-friendly code (Chapter 4). This is based on [124, 129].

- 3.1. Tensor contraction is a fundamental operation with applications in many domains, including machine learning and computational fluid dynamics. We derive a data layout for the tensor contraction kernel that reduces the number of shifts to the absolute minimum. For larger tensors where tiling becomes necessary to fit tensors into RTMs, we switch the data layout when bringing new tiles into RTM to eliminate the overhead shifts before loading new tiles (Section 4.1).

- 3.2. Motivated by our domain-specific transformations for the tensor contraction operation, we developed generalized

analysis and transformation schemes that examine a program's memory access pattern and identify potential loop candidates for transformations. Particularly, we target optimizing memory regions that are accessed more than once, as they are more likely to cause longer overhead shifts at the beginning of each new iteration (Section 4.2).

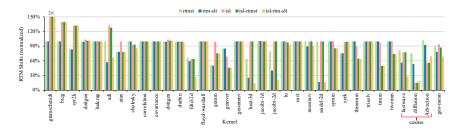

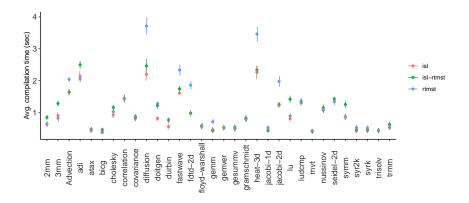

- 3.3. Based on our analysis, we transform the program loop structure (if it does not carry dependencies) or the data layout to eliminate the longer overhead shifts. We integrate our analysis and transformations into the mainstream LLVM polyhedral optimizer Polly and evaluate them on a set of more than 30 benchmark applications.

- 4. We explore the CIM capabilities of RTM by accelerating an entire hyperdimensional computing framework in RTM. We present HDCR or, HyperDimensional Computing in Racetrack, a complete in-RTM HDC system where all HDC operations, i.e., XOR, majority, rotate operation and bit counting are implemented in RTM using the RTM device characteristics. We use the basic principles of the TR operations, and together with intelligent data mapping and minimal changes to sense amplifier's circuitry, we implement the majority operation and population counting and rotate operations. More details on the proposed architecture and implementation are given in Chapter 5 and [130].

#### 1.6 OTHER CONTRIBUTIONS

In addition to the major contributions in the previous section, I have contributed to research works related to RTMs and beyond that are not part of this dissertation. For instance, in Section 4.1, we mainly focus on optimizations for the the on-chip RTM-based *scratchpad memory* (SPM). We have extended this work and proposed memory access reordering and layout transformation optimizations for the off-chip DRAM [128]. Similarly, we have investigated techniques exploiting domain knowledge and finding efficient layouts for decision trees in RTMs [83]. We proposed a *bi-directional linear ordering* (BLO) heuristic and proved that BLO can at most 4× worse compared to the optimal solution. Compared to our generic ShiftsReduce solution, BLO uses the access probabilities of decision tree nodes and finds layouts that, on average, incur 54% fewer shift operations. This is joint work with TU Dortmund.

In a recent work, we investigated the impact of shifts minimization on RTM reliability. Intuitively, shift optimization should indirectly improve RTM reliability. However, it was never investigated nor considered in the development of a reliability technique. We propose GROGU, a novel RTM reliability scheme that leverages the shift re-

duction from our generalized data placement scheme in Section 3.2 to provide efficient reliability with fewer resources [131]. Concretely, for two errors correction and three errors detection (2EC3ED), GROGU provides order-of-magnitude better reliability compared to the state-of-the-art reliability scheme. In addition, GROGU scales with nanowire length and can tune area overhead against shift distance to minimize latency impact compared to non-co-designed approaches, i.e., approaches that do not employ shift minimizations. This is joint work with the University of Pittsburgh and is currently under review.

Besides RTMs, I have contributed to research works targeting other emerging nonvolatile and conventional memory technologies. For instance, for memristors, we have developed the *open CIM compiler* (OCC), a fully automatic end-to-end compilation framework based on *multi level intermediate representation* (MLIR) rewriting, which allows reliable mapping of computational motifs to the memristors' crossbar in a transparent way, without any user intervention [268]. OCC exploits the layered abstractions of MLIR and implements high-level hardware-agnostic and low-level hardware-specific analysis and transformation passes. This is joint work with researchers from multiple organizations, including TU Eindhoven, Google, the University of Oklahoma, Edinburgh, and TU Dresden.

Further, I have contributed to efficient implementation of large size *last level caches* (LLCs) based on STT-RAM [346] and based on DRAM [85]. The latter benefits from a decoupled tag-data organization which mitigates the tag serialization latency by enabling concurrent accesses to the tag and data regions and minimizes the number of lookups and write access to the data region. To facilitate the evaluation of a hierarchal cache organization, we have extended the NVMain simulator to support multi-level cache systems [123]. Finally, to accelerate the memory-centric DNA seed location filtering algorithm in an NDP system, we recently employed a stacked DRAM architecture with dedicated memory and logic layers. We proposed algorithmic and hardware extensions that improve the overall system latency and energy consumption [84].

# UNDERSTANDING DEVICE PHYSICS AND SIMULATIONS

**Prelude:** This chapter introduces the main components of *racetrack memory* (RTM), including its cell structure, device physics, read-write mechanism, and prominent RTM architectures. It provides an overview of recent developments in RTMs and their application in the memory subsystem and optimizations. It also explains the RTM simulation tool that enables RTM design space exploration at various levels in the memory subsystem. The contents are based on our review article entitled "Magnetic racetrack memory: From physics to the cusp of applications within a decade" that was published in the *proceedings of the IEEE* in 2020 [22], and the racetrack memory simulator paper entitled "RTSim: A cycle-accurate simulator for racetrack memories" that was published in the IEEE *computer architecture letters* 2019 [125].

#### 2.1 MAGNETIC RACETRACK MEMORIES

Racetrack memory (RTM) is a novel spintronic memory-storage technology that has the potential to overcome fundamental constraints of existing memory and storage devices. It is unique in that its core differentiating feature is the movement of data, which is composed of magnetic domain walls (DWs), by short current pulses. This enables more data to be stored per unit area compared to any other current technologies. On the one hand, RTM has the potential for mass data storage with unlimited endurance using considerably less energy than today's technologies. On the other hand, RTM promises an ultrafast nonvolatile memory competitive with static random access memory (SRAM) but with a much smaller footprint. During the last decade, the discovery of novel physical mechanisms to operate RTM has led to a major enhancement in the efficiency with which nanoscopic, chiral DWs can be manipulated. New materials and artificially atomically engineered thin-film structures have been found to increase the speed and lower the threshold current with which the data bits can be manipulated. With these recent developments, RTM has attracted the attention of the computer architecture community that has evaluated the use of RTM at various levels in the memory stack. Recent studies advocate RTM as a promising compromise between, on the one hand, power-hungry, volatile memories and, on the other hand, slow, nonvolatile storage. By optimizing the memory subsystem, significant performance improvements can be achieved, enabling a new era of cache, graphical processing units, and high

capacity memory devices. In this article, we provide an overview of the major developments of RTM technology from both the physics and computer architecture perspectives over the past decade. We identify the remaining challenges and give an outlook on its future.

#### 2.1.1 Introduction

Conventional data storage and memory technologies are highly constrained by fundamental technology limits. As a result, a number of nonvolatile storage and memory technologies have emerged recently. The uninterrupted scaling and 3-D integration of NAND flash technology have enabled it to outperform hard disk drives (HDDs) in terms of volume and planar storage density [48]. However, its limited write endurance and higher erase and write latencies limit its applicability in future computing systems. Similarly, in memory technologies, phase change and magnetic memories have been proposed as candidate replacements for static random access memory (SRAM) and dynamic random access memory (DRAM) [239]. However, phase change memory (PCM) suffers from durability issues and its write latency is an order of magnitude higher compared to SRAM [239]. The spin-orbitronics-based magnetic racetrack memory (RTM) combines the best of all worlds, simultaneously offering endurance of magnetic HDDs, the density of 3-D vertical NAND flash, with the attractive latency rates of SRAM and DRAM [197, 221, 222]. A summary of qualitative and quantitative comparison of RTM with other technologies is presented in Table 2.1, which shows tradeoffs among various parameters that include latency, area, power, and retention characteristics.

RTM was first proposed in 2002 [219] and its fundamental underlying principle was first demonstrated in 2008 [221], [90]. Research studies over the past decade have led to unexpected physical mechanisms to operate RTMs. The information in RTM is stored in a magnetic track in which magnetic regions serve as bits, similar to HDDs. In contrast to the latter, RTM is neither limited to a 2-D design nor relies on the mechanical motion for operation. Instead, the magnetic bits are moved by electrical currents in which spin-polarized electrons interact with magnetic moments. As the motion is always along the electrical current, arbitrary pathways can be structured, making it possible to move bits in curved or even vertical wires [69]. Advances in spin-orbit mechanisms have led to different generations of RTM (see RTM 1.0–4.0 [222]), each characterized by leaps in the motion efficiency of the bits.

In this article, we review major breakthroughs and recent advances in the RTM technology starting from fundamental physics and materials science to the overall memory architecture. We focus on demonstrated experimental work of racetrack *domain wall* (DW) motion and materials used. We explain the data sensing and read/write mechanisms of the RTM access ports, organization of racetracks into arrays,

| ±341 = /                     | <b>J1</b>                  |                |                      |                  |        |             |                                   |                |                     |

|------------------------------|----------------------------|----------------|----------------------|------------------|--------|-------------|-----------------------------------|----------------|---------------------|

|                              | SRAM                       | DRAM           | STT-RAM              | RRAM             | PCM    | MRAM        | V-NAND                            | RTM            | HDD                 |

| Cell Size (F <sup>2</sup> )  | 120-200                    | 4-8            | 6-50                 | 4-10             | 4-12   | 10-60       | 1-5                               | ≤2             | 0.5                 |

| Write Endurance              | $\geq$ 10 $^{16}$          | $\geq 10^{16}$ | 4 x 10 <sup>16</sup> | 10 <sup>11</sup> | 109    | $> 10^{12}$ | 10 <sup>3</sup> - 10 <sup>5</sup> | $\geq 10^{16}$ | ≥ 10 <sup>16</sup>  |