Faculty of Computer Science

Center for Advancing Electronics Dresden Chair for Compiler Construction

#### Diploma Thesis

# Implementing an MLIR-based Compiler for In-DRAM Computing

#### Tianrui Zheng

Born on: 18th February 1998 in Shaanxi, China

Matriculation number: 4999374

to achieve the academic degree

Diplomingenieur (Dipl.-Ing.)

First referee

Prof. Dr.-Ing. Jeronimo Castrillon

Second referee

Dr.-Ing. Asif Ali Khan

Supervisors

Dr. João Paulo Cardoso de Lima Clément Fournier

Submitted on: 13th October 2025

TU Dresden Fakultät Informatik, Institut für Technische Informatik, Professur für Compilerbau

#### Task Description for Final Thesis (Diplomarbeit)

For: Tianrui Zheng

Degree program: Diplom Informationssystemtechnik

Matriculation number:

E-mail: tianrui.zheng@mailbox.tu-dresden.de

Implementing an MLIR-based compiler for in-DRAM Topic:

computing

In DRAM computing refers to a set of techniques that exploit architectural details of DRAM cells to perform computation directly in memory. This can offer great improvement in throughput, as it conceptually uses a DRAM module as an extremely large SIMD processing unit. Memory traffic is also greatly reduced, as data can stay in memory. On the other hand, DRAM cells only support very simple operations on bits, like majority gate, which can be used to build other simple logic gates. Larger instructions, like an adder, have to be built using many of these primitives, which increases latency.

Existing compilers for in DRAM like Chopper (Peng et al., 2023) use specific DSLs as input, and do not support automatic transformation of higher-level programs to compute in DRAM. The goal of this project is to create a new compiler that can take an arbitrary program as input, and convert parts of it to use in DRAM computing techniques where beneficial. The infrastructure for this compiler will be MLIR, as it will allow this compiler to be integrated in the wider MLIR ecosystem. The compiler IR will be generic and able to handle core arithmetic operations like those from the arith dialect. As a more specific frontend flow, integration within the CINM framework (Khan et al., 2022) should be considered as part of this project. An additional context element is the ongoing work on a C++-based in-DRAM compiler by Niklas Jungnitz at the Chair for Compiler Construction. This work could be used as a backend to generate memory controller instructions, and enjoy integration with the RTSim hardware simulation framework (Khan et al., 2019) for evaluation purposes.

For this project, the student should design an MLIR dialect or set of dialects to model in DRAM compute primitives. This should include conversions from higher-level operations (eg from the arith dialect) to those primitives. The dialects should be carefully designed to take advantage of SIMD-like capabilities of DRAM hardware. To evaluate this project, the student should gather quantitative data about the performance of their implementation for some applications (like GEMV, GEMM, or others), either through simulation or running on hardware. The thesis should compare these numbers to a CPU implementation, and if time allows, against a comparable framework like Chopper. An optional extension to this task would be to integrate the new dialects within the CINM framework. The student should also study select related work, and compare them qualitatively with their work.

Start: 12.05.2025 End: 13.10.2025

1<sup>st</sup> referee: Prof. Dr.-Ing. Jerónimo Castrillón

2<sup>nd</sup> referee: Dr.-Ing. Asif Ali Khan 1st supervisor: João Paulo Cardoso de Lima

2<sup>nd</sup> supervisor: Clément Fournier Jeronimo Castrillon Mazo

Digitally signed by Jeronimo Castrillon Mazo Date: 2025.05.08 06:00:49 +02'00'

Prof. Dr.-Ing. Jerónimo Castrillón (Professor in charge)

Martin Wollschlaeger Datum: 2025.05.12

Digital unterschrieben von Martin Wollschlaeger

Prof. Dr.-Ing. habil. Martin Wollschlaeger (Chairman of the Examination Board)

# Statement of authorship

I hereby certify that I have authored this document entitled *Implementing an MLIR-based Compiler for In-DRAM Computing* independently and without undue assistance from third parties. No other than the resources and references indicated in this document have been used. I have marked both literal and accordingly adopted quotations as such. There were no additional persons involved in the intellectual preparation of the present document. I am aware that violations of this declaration may lead to subsequent withdrawal of the academic degree.

Dresden, 13th October 2025

Tianrui Zheng

Faculty of Computer Science Chair for Compiler Construction

#### **Abstract**

Recent advances in deep learning, especially large language models (LLMs), have intensified the data movement bottleneck inherent in traditional Von Neumann architectures, where frequent transfers between compute units and memory dominate energy consumption and limit performance. Near- and in-memory computing address this challenge by relocating computation closer to or even inside memory, thereby reducing data movement and improving efficiency.

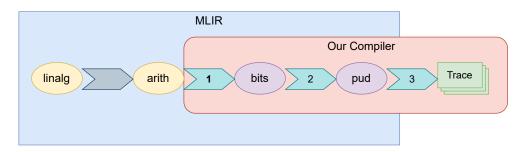

This thesis focuses on bit-serial in-DRAM computing. While prior frameworks have demonstrated its potential, they often rely on domain-specific languages or fixed programming patterns, limiting generality. To overcome this, this work develops a general-purpose MLIR-based compiler that lowers arithmetic and logical operations from the generic arith dialect into a new pud dialect, which represents bulkwise in-DRAM computation primitives. The backend targets computation-capable DRAM controllers to generate executable memory instruction sequences. Evaluation across diverse workloads shows that our compiler achieves comparable performance and energy efficiency to prior work. These results demonstrate the flexibility and extensibility of our MLIR-based framework as a general-purpose compilation flow for in-DRAM computing. Our code is publicly available at [Zhe25].

# **Contents**

| Αl | ostrac | ct      |                                  | VII |

|----|--------|---------|----------------------------------|-----|

| Sy | mbo    | s and A | Acronyms                         | ΧI  |

| 1  | Intr   | oductio | on                               | 1   |

|    | 1.1    | Motiva  | ation                            | 1   |

|    | 1.2    | Goal    |                                  | 3   |

|    | 1.3    | Struct  | sure of the Work                 | 3   |

| 2  | Bac    | kgroun  | d                                | 5   |

|    | 2.1    | DRAN    | M Basics                         | 5   |

|    |        | 2.1.1   | DRAM Organization                | 5   |

|    |        | 2.1.2   | Basic DRAM Operations            | 6   |

|    |        | 2.1.3   | DRAM Performance Characteristics | 7   |

|    | 2.2    | In-DR   | AM Computing                     | 7   |

|    |        | 2.2.1   | Ambit's Computing Substrates     | 8   |

|    |        | 2.2.2   | Row Address Organization         | 8   |

|    |        | 2.2.3   | AP and AAP Command Primitives    | 9   |

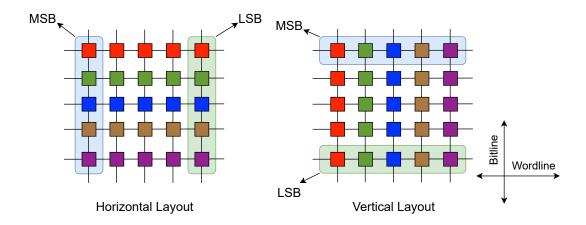

|    |        | 2.2.4   | Vertical Data Layout             | 9   |

|    | 2.3    | Toolch  | nain for In-DRAM Compilation     | 10  |

|    |        | 2.3.1   | Mockturtle                       | 10  |

|    |        | 2.3.2   | Lime                             | 11  |

|    | 2.4    | MLIR    |                                  | 11  |

|    |        | 2.4.1   | Dialects                         | 11  |

|    |        | 2.4.2   | Operations, Types and Attributes | 12  |

|    |        | 2.4.3   | Lowering                         | 12  |

| 3  | Rela   | ited W  | ork                              | 15  |

|    | 3.1    | SIMD    | RAM                              | 15  |

|    | 3.2    | MIME    | DRAM                             | 16  |

|    | 3.3    | CHOF    | PPER                             | 17  |

|    | 3 /    | Discus  | egion                            | 18  |

| 4 | Des  | ign and Implementation of the Compiler                        | 21 |

|---|------|---------------------------------------------------------------|----|

|   | 4.1  | Overview of the Compilation Flow                              | 21 |

|   | 4.2  | Bits Dialect                                                  | 22 |

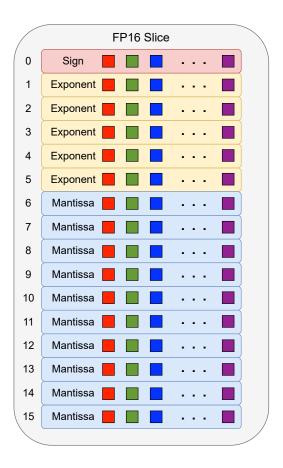

|   |      | 4.2.1 Slice Type                                              | 23 |

|   |      | 4.2.2 Operations                                              | 24 |

|   | 4.3  | PuD Dialect                                                   | 26 |

|   |      | 4.3.1 Row Type                                                | 26 |

|   |      | 4.3.2 Operations                                              | 27 |

|   | 4.4  | From Bits to PuD                                              | 27 |

|   |      | 4.4.1 Logic Synthesis                                         | 27 |

|   |      | 4.4.2 Address Allocation                                      | 29 |

|   |      | 4.4.3 Computation Process                                     | 31 |

|   | 4.5  | Operand Tracking                                              | 36 |

| 5 | Eval | luation                                                       | 39 |

|   | 5.1  | Computation Correctness Verification                          | 39 |

|   |      | 5.1.1 Verification Method                                     | 39 |

|   |      | 5.1.2 Accuracy of Floating-point Multiplication Approximation | 40 |

|   | 5.2  | Experimental Setup                                            | 40 |

|   |      | 5.2.1 Baseline Selection                                      | 40 |

|   |      | 5.2.2 Workloads Specification                                 | 41 |

|   |      | 5.2.3 NVMain-PIM Simulator                                    | 41 |

|   |      | 5.2.4 Trace Emitting                                          | 42 |

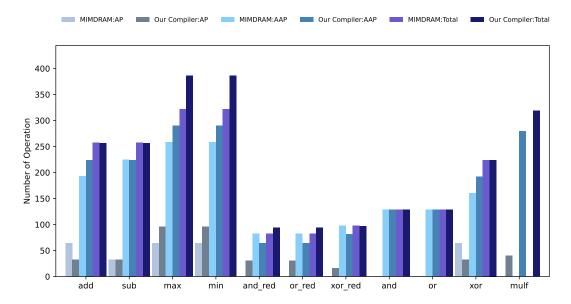

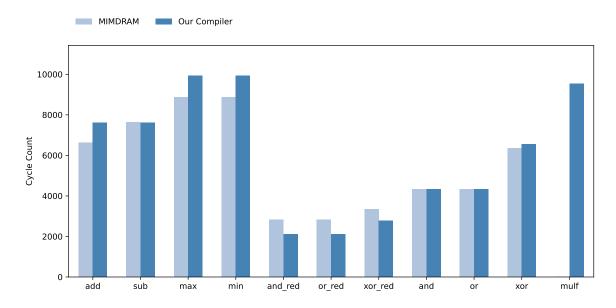

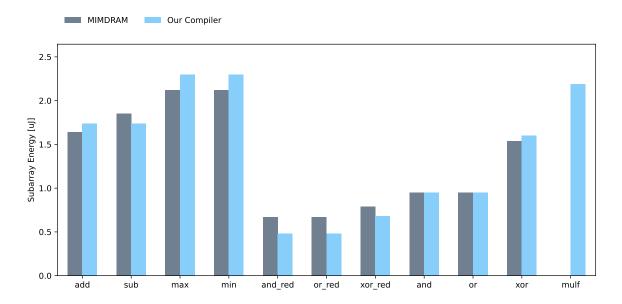

|   | 5.3  | Results Analysis                                              | 43 |

| 6 | Con  | clusion and Further Work                                      | 47 |

|   | 6.1  | Future Work                                                   | 48 |

|   |      | 6.1.1 Flexible Data Layout and Configuration                  | 48 |

|   |      | 6.1.2 Bank-Level Parallelism                                  | 49 |

|   |      | 6.1.3 Advanced Data Mapping                                   | 49 |

|   |      | 6.1.4 Additional In-DRAM Computing Back-ends                  | 49 |

|   |      | 6.1.5 Summary                                                 | 50 |

| 7 | Δck  | nowledgements                                                 | 51 |

# **Symbols and Acronyms**

| AAP            | ACTIVATE; ACTIVATE;                        | IR              | Intermediate Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | PRECHARGE                                  | $\mathbf{LLM}$  | Large Language Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AI             | Artificial Intelligence                    | LSB             | Least Significant Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AIG            | AND-Inverter Graph                         | MIMD            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AP             | ACTIVATE; PRECHARGE                        | MIMD            | Multiple Instructions, Multiple Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| API            | Application Program Interface              | MSB             | Most Significant Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ASIC           | Application-Specific Integrated<br>Circuit | MIG             | Majority-Inverter Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CNN            | Convolutional Neural Network               | MLIR            | Multi-Level Intermediate<br>Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CPU            | Central Processing Unit                    | NVM             | Non-Volatile Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DCC            | Dual-Contact Cell                          |                 | , and the second |

| DNN            | Deep Neural Network                        | OS              | Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DRAM           | Dynamic Random-Access                      | PUD             | Processing-Using-DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Memory                                     | RRAM            | Resistive Random-Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DSA            | Domain-Specific Accelerator                |                 | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DSP            | Digital Signal Processor                   | SIMD            | Single Instruction, Multiple<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DSL            | Domain-Specific Language                   | $\mathbf{SRAM}$ | Static Random-Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FCFS           | First-Come, First-Serve                    | SSA             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FRFCFS         | First-Ready, First-Come,                   |                 | Static Single-Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | First-Serve                                | TPU             | Tensor Processing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\mathbf{FP}$  | Floating-Point                             | TRA             | Triple-Row Activation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\mathbf{GPU}$ | Graphics Processing Unit                   | XIG             | XOR-Inverter Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                |                                            |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### 1 Introduction

#### 1.1 Motivation

For many years, Moore's Law [Moo65] - the idea that the number of transistors on a chip doubles roughly every two years - drove the steady growth of computing performance. However, as transistors approach their physical limits, the benefits of Moore's Law have been fading, marking the transition to what is often called the *post-Moore era* [ITR15; Wal16]. Even more critically, Dennard scaling [Den+74] - the principle that power density stays constant as transistors shrink - broke down in the early 2000s. As a result, further increases in clock frequency caused excessive power use and heat generation, bringing the steady rise in single-core performance to a halt [Esm+11].

To address these limitations, the semiconductor industry has increasingly shifted toward **Domain-Specific Accelerators (DSAs)**, which achieve superior performance and energy efficiency by tailoring hardware to specific application domains. Examples include:

- Graphics Processing Units (GPUs), initially designed for rendering graphics but later exploited for highly parallel workloads such as deep learning training and inference

- **Digital Signal Processors (DSPs)**, optimized for embedded and mobile markets, often consuming only 10% of the power of a typical x86 Central Processing Unit (CPU) while providing significantly better floating-point performance per watt [Ham+10]

- Tensor Processing Units (TPUs), custom Application-Specific Integrated Circuits (ASICs) by Google, which deliver substantial speedups for neural network inference by exploiting matrix-multiplication workloads [Jou+17]

These examples reflect a broader trend: as scaling of general-purpose CPUs slows, specialized hardware has become the main path to sustaining gains in performance and energy efficiency. Industry reports identify DSAs as a key driver of innovation in the post-Moore era [McK20; Kha+24], and academic research likewise highlights their growing role in areas ranging from high-performance computing to machine learning [Nie+24; Hu+25].

In recent years, advances in machine learning, particularly Convolutional Neural Networks (CNNs) and more recently Large Language Models (LLMs), have driven remarkable breakthroughs across Artificial Intelligence (AI). These models have achieved state-of-the-art

results in domains ranging from image classification and object detection to natural language understanding and generation [KSH17] [Dev+19]. At the same time, the training phase of such models has grown increasingly demanding. Training a modern LLM, for instance, may require hundreds of billions of parameters and terabytes of training data, translating into exaflop-scale computations sustained over weeks on large GPU clusters [Nar+21].

These characteristics impose new and stringent requirements on hardware. On the one hand, the enormous volume of parallel computation has fueled the adoption of massively parallel accelerators such as GPUs and TPUs, which can deliver the necessary throughput for matrix-multiplication-dominated workloads. On the other hand, the **data-centric** nature of machine learning exposes severe memory bottlenecks: moving large tensors between compute cores and off-chip Dynamic Random-Access Memory (DRAM) consumes substantial energy and limits overall system efficiency. It has been reported that data movement, rather than computation, accounts for 40–60% of total system energy consumption in many machine learning workloads [Hor14]. As model sizes continue to grow, these bottlenecks increasingly dominate both performance scaling and energy consumption, motivating new architectural paradigms such as near-memory and in-memory computing.

The central idea behind near-memory and in-memory computing is to reduce the costly data movement between processing units and memory, which has become the dominant factor in both performance and energy consumption. The former integrates compute units close to the memory banks or within the memory controller. By reducing the distance data must travel, near-memory computing relieves the memory bandwidth wall and lowers energy overhead. In-memory computing goes one step further by embedding computation directly inside the memory arrays themselves. In this paradigm, memory cells can be repurposed to perform simple arithmetic or bit-wise operations, thereby eliminating most data transfers [Lim+24; Lim+25].

A particularly promising branch of in-memory computing is in-DRAM computing, which leverages the intrinsic analog behavior of DRAM circuitry to perform operations directly within the memory arrays. Unlike near-memory computing, which integrates logic units into the memory controller or 3D-stacked memory logic layers, in-DRAM techniques exploit existing DRAM structures such as sense amplifiers and row buffers to realize data movement and bit-wise operations with minimal changes to commodity DRAM chips.

Representative works demonstrate the efficiency of this approach. [Ses+13] performs bulk data copy and initialization entirely inside DRAM through row-buffer transfers, achieving up to  $11\times$  lower latency and  $74\times$  lower energy than copying using CPU. [Ses+16] extends this idea to bulk bit-wise operations by exploiting Triple-Row Activation (TRA), yielding  $10-25\times$  higher throughput and  $25-59\times$  lower energy compared to conventional execution. [Ses+17] further generalizes in-DRAM bit-wise acceleration with modest hardware overhead (<1% DRAM area), improving throughput and energy efficiency by  $32\times$  and  $35\times$  respectively. These results highlight the main advantage of in-DRAM computing: it directly eliminates costly data transfers over the memory channel while utilizing the full internal bandwidth of DRAM subarrays.

Beyond early primitives above, a number of works have sought to extend this in-DRAM computing paradigm toward more general or domain-specific acceleration. For example, [Haj+21] and [Oli+24] propose a general-purpose Single Instruction, Multiple Data (SIMD)

and Multiple Instructions, Multiple Data (MIMD) execution model. By packaging sequences of memory instructions such as TRAs and Row-Clones into micro-programs ( $\mu$ Programs), it supports a broad range of bit-wise and arithmetic kernels in a programmable fashion. Another representative effort is [PWY23], which emphasizes flexible in-DRAM acceleration for machine learning workloads. It proposes a high-level programming model that maps neural network operators onto in-DRAM bit-serial execution.

Nevertheless, they share a common limitation: their programmability is tightly coupled to specific domains, operators, or Domain-Specific Languages (DSLs). [Haj+21] and [Oli+24] expose programmability only through predefined bit-serial kernels (C macros), while [PWY23] (its compiler is built upon a DSL named Usuba [MD19]) and related frameworks are restricted to neural networks. As such, they lack the generality and flexibility required for serving as a compiler backend across diverse application domains. This observation motivates this work: to design a general-purpose compilation flow, based on Multi-Level Intermediate Representation (MLIR) framework, that bridges high-level arithmetic operations and low-level in-DRAM primitives in a systematic and extensible manner.

#### 1.2 Goal

The goal of this work is to develop an MLIR-based compiler targeting bit-serial bulkwise in-DRAM computing.

To ensure generality and flexibility, our compiler adopts the arith dialect as the front-end, since within the MLIR ecosystem it serves as a generic representation of arithmetic and logical operations. For instance, operations defined in machine learning frameworks such as **PyTorch** can be lowered via torch-mlir into the linalg dialect, from which fundamental operators are further lowered into arith representation, augmented with the scf or affine dialects to capture control flow and loop information.

This work introduces two new dialects to describe bulkwise in-DRAM computing primitives, thereby exploiting the bit-serial, SIMD-like massive parallelism inherent in this computing model. On the back-end, the compiler targets DRAM controllers augmented with computation capabilities, ultimately generating memory instruction sequences for computation, exemplified by primitives such as ACTIVATE; PRECHARGE (AP) and ACTIVATE; ACTIVATE; PRECHARGE (AAP).

For evaluation, this work compares against prior efforts such as Chopper [PWY23] and MIMDRAM [Oli+24]. Specifically, we assess the generated memory instruction sequences for equivalent workloads, and analyze performance and energy efficiency metrics obtained through simulation.

#### 1.3 Structure of the Work

The remainder of this thesis is organized as follows.

Chapter 2 provides the necessary background for understanding the work. It first introduces the organization, basic operations, and performance characteristics of DRAM, and then reviews in-DRAM computing with a focus on Ambit's computing substrates and related primitives. The chapter also presents the tool-chain employed in this thesis, including the mockturtle logic synthesis framework and the Lime code generator, before concluding with an overview of MLIR and its dialect-based compilation infrastructure.

Chapter 3 surveys related work. We discuss SIMDRAM [Haj+21] and MIMDRAM [Oli+24] as two representative programmable frameworks for in-DRAM computing, and CHOPPER [PWY23] as the most closely related compiler-based approach. The chapter concludes with a summary highlighting the differences between prior work and our MLIR-based compiler.

Chapter 4 presents the design and implementation of our compiler. It outlines the overall compilation flow and introduces the newly designed bits and pud dialects. Furthermore, it details the progressive lowering from high-level arithmetic operations to in-DRAM instruction sequences, covering logic synthesis, address allocation, computation process, and operand tracking.

Chapter 5 evaluates the proposed compiler. We first verify computation correctness and analyze the approximation accuracy of Floating-Point (FP) multiplication. We then describe the experimental setup, including workload specification, simulator configuration, and trace emitting, followed by a detailed analysis of performance and energy results compared to prior work.

Finally, Chapter 6 concludes the thesis and outlines directions for future research.

## 2 Background

Modern in-memory computing techniques frequently rely on the fundamental behavior and internal structure of DRAM. To motivate the architectural mechanisms exploited later in this work, we first revisit the basics of commodity DRAM organization and operation. This section outlines the hierarchical layout of DRAM, its core access primitives, and the timing and performance characteristics that shape both its traditional role as main memory and its emerging use as a substrate for computation.

#### 2.1 DRAM Basics

Dynamic Random-Access Memory (DRAM) is the predominant technology used in modern main memory systems due to its high density, low cost per bit, and relatively low idle power consumption. Although DRAM is conceptually simple - storing each bit as charge in a capacitor - its internal organization and operation involve multiple layers of hierarchy and complex timing constraints. A proper understanding of DRAM structure and access mechanisms is essential for analyzing both its limitations and its potential for architectural extensions. This section provides an overview of the fundamental organization, operations and performance characteristics of commodity DRAM.

#### 2.1.1 DRAM Organization

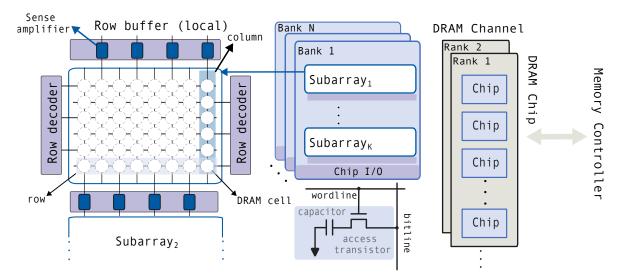

As shown in Figure 2.1, DRAM system is organized hierarchically. At the top level, a memory channel provides a physical interface between the memory controller and one or more DRAM modules. Each module typically consists of multiple ranks, where a rank is a set of DRAM chips that operate in lockstep to provide a wide data bus (e.g., 64 bits). Within each rank, the storage is divided into multiple banks (commonly 8-16 in DDR4/DDR5 systems). Banks are the fundamental units of parallelism: different banks can be activated and accessed independently, allowing overlap of memory requests.

Each bank is further subdivided into multiple **subarrays**. A subarray is a two-dimensional array of DRAM **cells**, typically organized into thousands of rows and columns. Each row spans across the subarray and connects to a set of sense amplifiers, collectively known as the **row**

Figure 2.1: Overview of DRAM Organisation [Lim+26]

**buffer**. When a row is activated, the contents of the entire row are transferred into the row buffer, from which individual columns can be read or written.

Within each subarray, the basic storage element is the DRAM **cell**, consisting of a single capacitor and an access transistor. The transistor connects the capacitor to the bit-line when enabled by a word-line. Since capacitors are leaky, DRAM cells must be periodically refreshed to restore their charge, typically every 32–64 ms. The cell's simplicity allows extremely high density, but also makes it volatile and slower to access compared to Static Random-Access Memory (SRAM).

Some modern DRAM chips further group subarrays into smaller two-dimensional structures called **mats**. A mat consists of hundreds of rows and columns, with its own local sense amplifiers. The mats are tiled to form a full subarray, and global interconnects coordinate their operation. This mat-level structure is not visible to software but is important for understanding access granularity and potential internal parallelism.

#### 2.1.2 Basic DRAM Operations

Accessing DRAM involves a sequence of fundamental operations orchestrated by the memory controller. The three key commands are activate, read/write, and precharge.

Activate (ACT): An activate command opens a row by raising its word-line, thereby connecting all cells in that row to their respective bit-lines. The tiny charge stored in each capacitor slightly perturbs the bit-line voltage. The corresponding sense amplifier then detects this deviation, amplifies it to a full logic level, and stores the value in the row buffer. At the same time, the sense amplifier refreshes the charge in the capacitor, restoring the data. Once a row is activated, it remains in the row buffer until explicitly precharged.

Read/Write (RD/WR): After a row is active, read and write operations can be issued to access specific columns within the row buffer. A read copies the data from the sense amplifier to the I/O bus, while a write updates both the sense amplifier and the underlying cell. Since the entire row is already sensed and buffered, column accesses are relatively fast as long as they target the currently open row.

**Precharge (PRE)**: To access a different row within the same bank, the current row must first be closed. This is achieved by precharging, which restores the bit-lines to a neutral voltage and disconnects the active word-line. Only after precharge can another activate be issued in the same bank. The precharge step ensures signal integrity but adds latency to row-to-row accesses.

**Refresh (REF).** Because charge in the capacitors leaks over time, DRAM requires periodic refresh operations to prevent data loss. A refresh essentially re-activates and restores the charge of rows across all banks on a fixed schedule (e.g., every 64 ms). Refresh operations occupy memory cycles and contribute to both energy consumption and performance variability.

#### 2.1.3 DRAM Performance Characteristics

From a system perspective, DRAM performance is shaped by the interaction of row buffers, bank-level parallelism, and refresh overheads. A key factor is whether an access results in a **row buffer hit** (the requested row is already active), a **row buffer miss** (the bank is idle and a new row must be activated), or a **row buffer conflict** (a different row is currently active and must be precharged before the new row can be activated). Row buffer hits yield the lowest latency and energy, while conflicts incur the highest overhead due to the full precharge—activate sequence.

Bank-level parallelism allows simultaneous accesses to different banks, partially hiding individual bank latencies. However, the global memory channel bandwidth still limits overall throughput, as all banks within a channel share the same I/O interface. Subarray-level parallelism has also been proposed in research, where subarrays within the same bank can be activated independently to increase concurrency, though commodity DRAM typically restricts one active row per bank at a time.

Energy consumption in DRAM is dominated by three sources: activating rows (charging large word-lines and bit-lines), refreshing cells, and transferring data across the off-chip bus. Among these, data movement between DRAM and the processor is often the most expensive, motivating the exploration of architectures that reduce such transfers.

#### 2.2 In-DRAM Computing

This section introduces the core ideas behind in-DRAM computing as Ambit proposed in [Ses+17], an in-memory accelerator that performs bulk bit-wise operations directly within commodity DRAM arrays by carefully orchestrating multi-row activation and sense amplification. We first explain Ambit's compute substrate and primitive operations, then describe the row-address organization and command sequences that make these operations practical, and finally discuss data layout considerations (especially the vertical layout used by bit-serial SIMD computation).

#### 2.2.1 Ambit's Computing Substrates

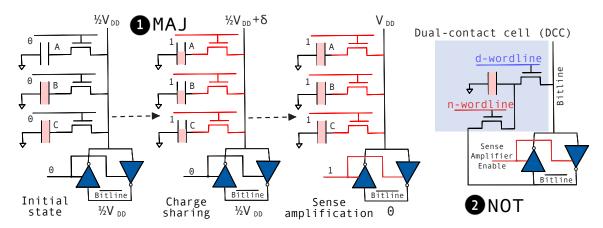

Ambit's central observation is that simultaneously activating three rows that share a sense amplifier causes the bit-line to resolve to the **majority** value of the three storage capacitors connected to that bit-line. As shown in Figure 2.2, this follows from (i) charge sharing from the precharged bit-line to the three capacitors and (ii) the positive feedback of the cross-coupled inverters that complete sensing: if at least two of the three cells are charged (or discharged), the sense amplifier resolves to 1 (or 0), and all three cells are then overwritten with that majority value. Ambit exposes this as a Triple-Row Activation (TRA), which implements a 3-input majority operation MAJ on every bit-line in parallel. Formally,  $MAJ(A, B, C) = A \cdot B + A \cdot C + B \cdot C$ .

Figure 2.2: Majority and Not Logic Implementation of Ambit [Lim+26]

Because MAJ is functionally complete with a constant input, Ambit realizes bit-wise AND and OR by using a third "control" row that is pre-initialized to all-zeros or all-ones:  $MAJ(A, B, C_0) = A \wedge B$  and  $MAJ(A, B, C_1) = A \vee B$ . To support this efficiently, Ambit reserves two special control rows per subarray,  $C_0$  (all 0s) and  $C_1$  (all 1s), which can be selected via dedicated control-row addresses.

Ambit implements NOT with a **Dual-Contact Cell (DCC)**. As presented in Figure 2.2, DCC connects a single storage capacitor to either side of the cross-coupled sense amplifier through two independent word-lines, commonly referred to as the **d**- and **n**- word-lines. By first activating a source row to let the sense amplifier resolve to the source value and then activating the DCC's **n**-word-line, Ambit forces the capacitor connected through the complementary side of the sense amplifier to charge to the inverted value. The bank is then precharged, and a Row-Clone copy moves the inverted data from the DCC's **d**-side into the destination row. Ambit's controller sequences these steps as:  $ACT(src) \rightarrow ACT(DCC_n) \rightarrow PRE \rightarrow Row-Clone(DCC_d \rightarrow dst)$ .

#### 2.2.2 Row Address Organization

To make in-DRAM computation practical and to keep the software-visible address space contiguous, Ambit partitions the row addresses inside each subarray into three disjoint groups:

• **B-Group** (bitwise/computation rows), containing designated TRA rows  $(T_0-T_3)$  and DCC rows;

- C-Group (control rows), two rows  $C_0$  and  $C_1$  that store all-zeros and all-ones;

- **D-Group** (data rows), which hold regular application data and are the only rows exposed to the Operating System (OS) and applications.

A small B-group row decoder maps a set of reserved B-addresses (e.g., B0-B15) to one or multiple physical word-lines, enabling single-, double-, or triple-row activation with a single address. For example, addresses B12-B15 simultaneously drive three word-lines for TRA, while B8-B11 activate two word-lines to aid in result duplication. The B-group decoder provides addresses that directly trigger double/triple activations (e.g., a single B12 may assert three rows  $T_0$ ,  $T_1$ , and  $T_2$ ), minimizing controller overhead while preserving commodity interfaces. This grouping is widely adopted in subsequent work as the canonical Ambit layout (B/C/D groups).

#### 2.2.3 AP and AAP Command Primitives

Ambit introduces two composite command sequences that the memory controller issues to DRAM:

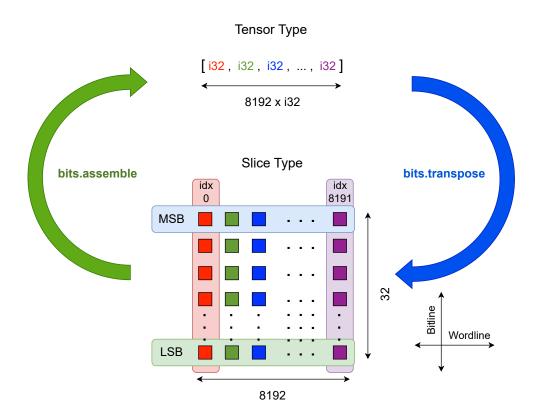

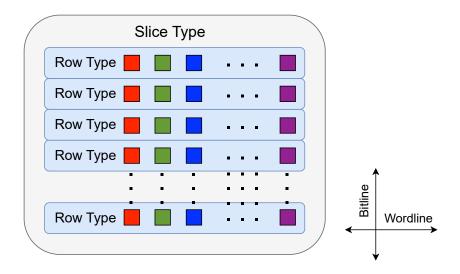

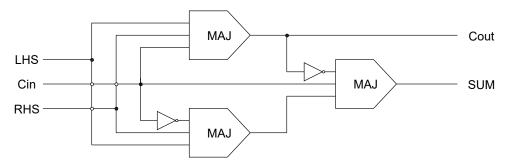

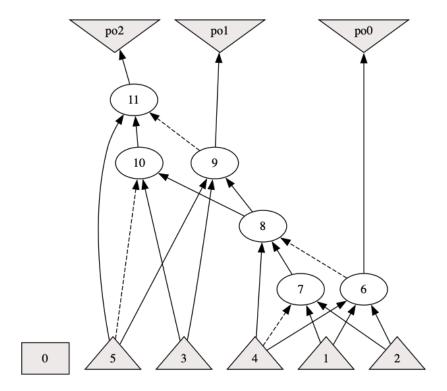

- ACTIVATE; PRECHARGE (AP) A multi-row activation (e.g., TRA for MAJ) followed by a PRE to close the bank. AP encapsulates logic operations (e.g., MAJ/AND/OR) that intentionally activate multiple rows before a precharge;