Chair News

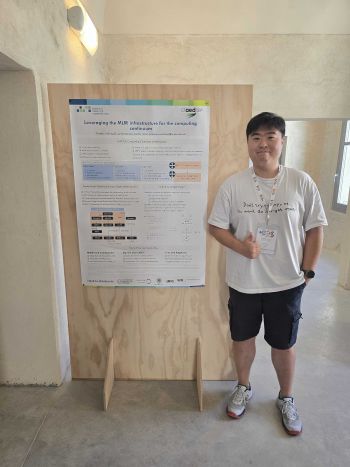

Invited talk on Near Memory Computing ABUMPIMP @ Euro-Par 2024

Read more … Invited talk on Near Memory Computing ABUMPIMP @ Euro-Par 2024

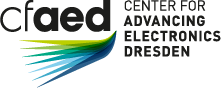

CC Chair at DAC'24

Published on

The CC Chair participated in the Rewe Team Challenge 2024

Read more … The CC Chair participated in the Rewe Team Challenge 2024

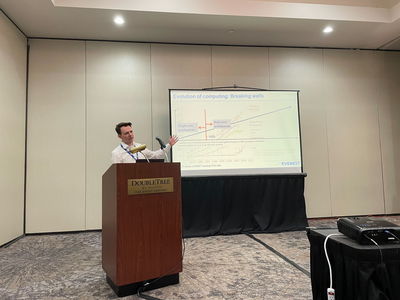

Felix Suchert and part of the EVEREST Team at FCCM’24

Read more … Felix Suchert and part of the EVEREST Team at FCCM’24

Page 3 of 17